- 2018-1-16

- ニュース, 技術ニュース, 電気・電子系

- ゲート変調イメージング技術, プリンテッドエレクトロニクス, 産業技術総合研究所

印刷法で製造したデバイスの高品質化に向けた非破壊インライン検査技術

産業技術総合研究所(産総研)は2018年1月15日、独自に開発した薄膜トランジスタ(TFT)アレイ一括検査技術の測定感度と検査面積を大幅に向上させるとともに、同技術を応用したストレージキャパシター(電荷を蓄積したり放出したりできる素子)の検査を可能にしたと発表した。

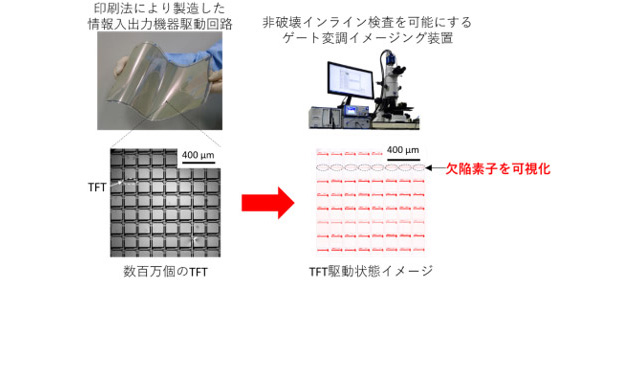

軽量で柔軟なプラスチックフィルム上に印刷技術を用いてデバイスを製造するプリンテッドエレクトロニクス技術は、ディスプレーやタッチパネルなど情報入出力機器の製造技術として期待されている。しかし数百万個のTFTとストレージキャパシターがアレイ状に配置された情報入出力機器の駆動回路(アクティブバックプレーン)の短時間での検査は難しく、高生産効率と高品質を両立させる上での課題となっていた。

産総研ではこれまで、バックプレーン上のTFTアレイの駆動状況を光学イメージ化して高速に一括して検査できる「ゲート変調イメージング技術」の開発を進めてきた。これを改良して今回、測定感度と検査面積の向上と、同技術を応用したストレージキャパシターの検査に取り組んだ。

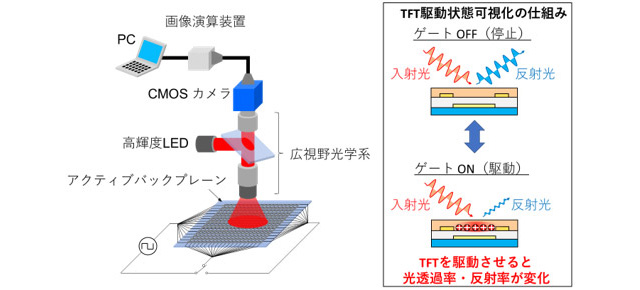

ゲート変調イメージング装置では、アクティブバックプレーンの全てのTFTにゲート電圧をかけた状態(TFTを駆動した状態)と、かけない状態(TFTを停止させた状態)の光学イメージをそれぞれ撮影。両者の差分イメージを求めて微小な変化のイメージ(ゲート変調イメージ)を得る。正常動作するTFTだけがゲート変調イメージに現れるので、動作不良個所をイメージから一括して特定できる。

ゲート変調イメージング装置の概略と、TFTの駆動状態を可視化する仕組み

今回、ゲート変調イメージの演算とSN比向上のための積算を、毎秒約1GBのデータ処理速度で光学イメージの撮影と同時に実行できる画像演算装置を新たに開発。これを高解像度・高フレームレートのCMOSカメラと組み合わせ、イメージの解像度と単位時間当たりの積算回数を、これまでの11万画素・毎秒15回から415万画素・毎秒45回へと大きく向上させた。

イメージのSN比は積算回数の平方根に比例するため、単位時間当たりの積算回数の増加により測定感度が向上する。また高解像度化により、一括検査できる面積が大幅に増加し、一括検査できる面積は従来の1mm角から3cm角に向上した。さらに、これまでの装置では十分なSN比のゲート変調イメージを得るのに10分以上かかったのに対し、今回の装置では3分以内に同程度のSN比のイメージを得ることができたという。

今回開発したゲート変調イメージング装置を用いて、各画素にTFTとストレージキャパシターをひとつづつ配置したアクティブバックプレーン(画素密度150ppi、全印刷により製造)の検査を実施。広い範囲に含まれる多数のTFTを一括検査し、動作不良のTFTを特定できるとともに、絶縁不良のキャパシターについても、広い面積範囲を一括検査できることが確認された。今回の装置では、150ppiのアクティブバックプレーンの場合には、最大3cm角の範囲のTFT(とストレージキャパシター)約3万素子を3分以内に一括検査できる。

今後産総研では、今回開発したゲート変調イメージング技術を用いた非破壊インライン検査技術により、電子ペーパーなどを対象とした印刷製造ラインへの実装に向けた実用化研究に取り組むという。