ノースカロライナ州立大学の研究グループが、より少数のトランジスタで多数の機能を実行可能にする新しい非線形カオス型集積回路を開発した。この集積回路は同じ1つの回路で異なるタスクを実行できるため、トランジスタの数を増やさずともコンピュータ・チップの処理能力を向上できるという。

半導体に積まれるトランジスタの集積率は18~24カ月で2倍になる——。いわゆる「ムーアの法則」だ。実際に少し前までは、個々のトランジスタのサイズを小さくし、可能なだけ多くのトランジスタをチップに集積させることで、この法則どおりに半導体の性能は向上してきた。

しかし、トランジスタをこれまで以上に縮小しようにも、物理学の限界に達しつつある。この手法が早晩使えなくなると予想されるため、半導体産業は優れたコンピュータ・チップを創り出す新しい手法を探している。その手法となり得るのが、今回開発された非線形カオス型集積回路だ。

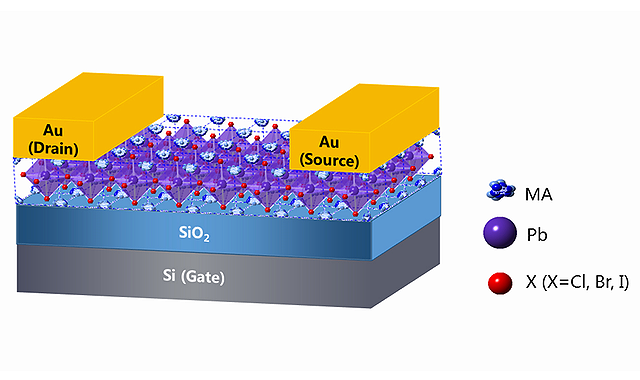

トランジスタ回路は通常、各々が1つのタスクに対応している。コンピュータ・プロセッサは、各々の命令と被演算子を集積回路上の適切なトランジスタ回路に送り込み、そこで命令を実行する。

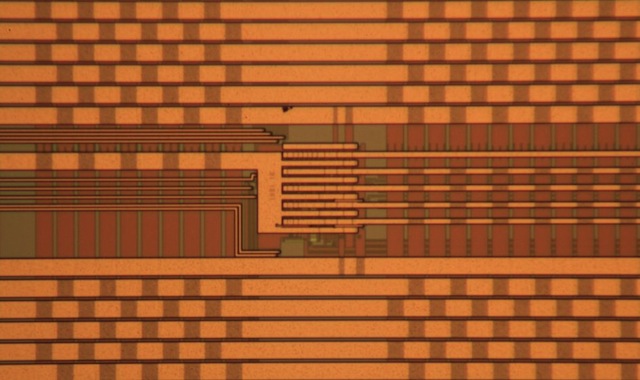

それに対して、ノースカロライナ州立大学物理学科の研究員たちは非線形カオス理論を活用し、異なるタスクを実行できるようにトランジスタ回路をプログラムした。非線形トランジスタ回路は、非常に多くの回路パターンが含まれ、異なる機能を担う異なる回路パターンが共存する。その上、機能の選択が可能だ。そのため、異なる命令を実行できるようにプログラムし、再構成することができる。

言い換えると非線形トランジスタ回路は、異なる動作と機能を実行できるようにモーフィング変形できることになる。同じ回路において異なる処理タスクを実行できるため、より少数のトランジスタで多くのタスクを処理できるのだ。

ノースカロライナ州立大学物理学科のWilliam Ditto教授は、「この研究におけるチップ・サイズと能力、プログラミング性は商品化レベルに近づきつつある。デザインと製造に関する3カ月サイクルの改善・実行によって、数カ月以内に商品化実現性について重要な成果を得るだろう」と語っている。

関連リンク

Reconfigurable Chaos-based Microchips Offer Possible Solution to Moore’s Law