- 2017-3-1

- ニュース, 制御・IT系, 製品ニュース

- Protium S1, ケイデンス, ケイデンス・デザイン・システムズ, プロトタイピングプラットフォーム

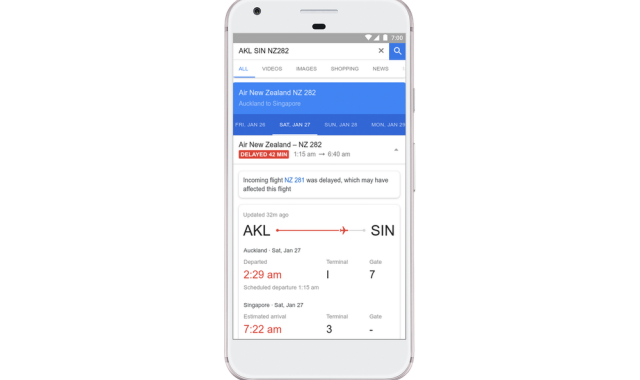

米ケイデンス・デザイン・システムズは2017年2月28日、検証立ち上げ期間を短縮できるProtium S1 FPGAベースプロトタイピングプラットフォームを発表した。

同プラットフォームは、同社のPalladiumZ1エンタープライズエミュレーションプラットフォームと前処理工程を共通化することにより、一般的なFPGAプロトタイピング手法よりも検証立ち上げ期間を短縮できるという。

またXilinx Virtex UltraScale FPGAテクノロジーを利用することによって、従来製品と比較して対応する設計規模が6倍、性能が平均2倍、それぞれ向上している。

同プラットフォームは、高度なメモリモデリング、インプリメンテーション機能でプロトタイプ立ち上げ期間を短縮する、Palladium Z1プラットフォームと共通のコンパイルフローを共用して既存の検証環境を最大80%再利用できるなどの特徴を持つ。

また、メモリのバックドアアクセスや複数のFPGAにまたがる波形表示、フォース/リリース、ランタイムクロック制御などのファームウエアやソフトウエアの生産性を向上させるデバック機能を備えるという。