- 2016-9-20

- ニュース, 制御・IT系, 製品ニュース

- ASIC, DDR3 SDRAM, Easy Prototyping, FFSA, FPGAプロトタイピング, MorethanIP, Northwest Logic, PCI Express, カスタムSoC, 東芝

東芝は2016年9月12日、カスタムSystem on Chip(SoC)開発に不可欠な「FPGAプロトタイピングの設計資産再利用」を容易にするカスタムSoCソリューション「Easy Prototyping」の提供を開始した。同ソリューションを用いれば、FPGAプロトタイピングからカスタムSoC開発までの開発工期を大幅に短縮できるという。

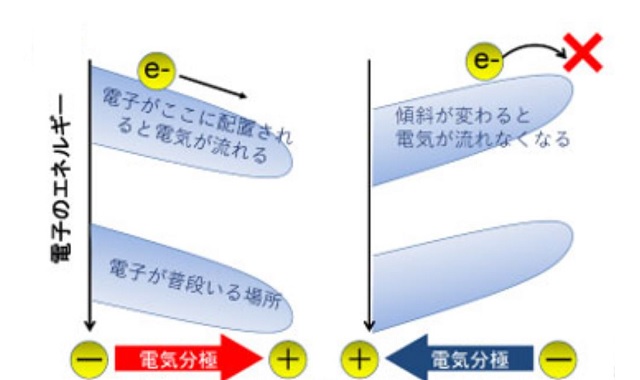

ASIC開発の大規模化や複雑化、費用肥大化に伴い、開発リスク低減やソフトウェア開発期間確保のために、FPGAプロトタイプによるソフトウェア並行開発への要求が高まっている。だが、一般的なFPGAプロトタイピングでは、FPGAを前提としたライブラリやIPを使用して設計するため、カスタムSoC化する場合はハード/ソフト共に再設計が必要だ。

FPGA用IPはASICやFFSAでは使用できず、FPGAプロトタイプと量産品(ASIC・FFSA)ではRTLが異なる。そのため、FPGAプロトタイピングの設計資産を再利用するには、「量産品とは別にFPGAプロトタイプ専用のRTLを作成」「FPGAプロトタイプ上で開発したソフトウェアの一部を量産用に書き換え・再試験」という手間が欠かせなかった。

一方、Easy Prototyping対応のライブラリやIPサブシステムを利用して設計すると、FPGAプロトタイプと量産向けASIC/FFSAの両方に対応したRTLを容易に作成できる。そのため、FPGA向けに開発したハード/ソフト設計資産のカスタムSoC開発への再利用が容易になる。

IPサブシステムには、FPGAで実績のあるサードパーティ製IPなど、FPGAとの親和性が高いIPを採用。Easy Prototypingに対応するIPサブシステムは現在、MorethanIPの10ギガビットイーサネットのほか、Northwest LogicのPCI Express3.0/2.1/1.1とDDR3 SDRAMコントローラの利用が可能だ。東芝はIPサブシステムのラインナップを順次拡大していくとしている。