- 2016-9-16

- ニュース, 制御・IT系, 製品ニュース, 電気・電子系

- ザインエレクトロニクス, 完全デジタル型CDR技術, 東京大学

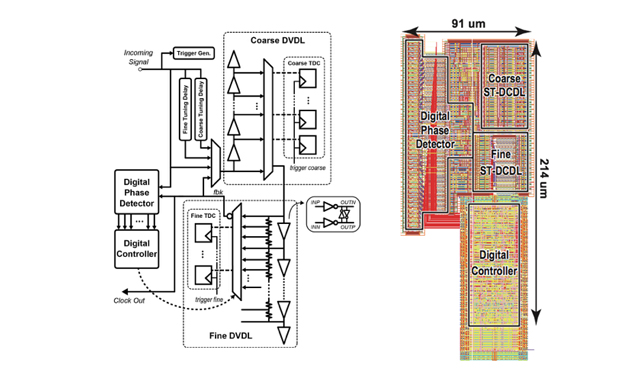

ザインエレクトロニクスは9月15日、東京大学との共同研究で開発した「耐ノイズ高速起動完全デジタル型クロック・データ・リカバリ(CDR)技術」を発表した。

同社は東京大学との共同研究において、モバイル機器などのアプリケーションの特徴であるバースト・モード(モバイル機器の動作パターンの断続的な状態)に対応して、待機時消費電力と復帰速度に優れた完全デジタル型CDR技術をすでに開発していた。

今回新たに開発された完全デジタル型CDR技術では、以前開発した完全デジタル型CDR技術の特徴を受け継がせつつ、起動後の位相同期回路(PLL)の動作を工夫し、デジタル型CDR回路のノイズ耐性を向上。データ復調時の失敗の原因となるノイズの影響を解消し、定常状態の安定動作を可能にした。

今回の完全デジタル型CDR技術は、複合構成型デジタル可変遅延素子や位相検出・制御回路で構成される新規周波数追従機能を搭載することで、入力信号の立ち上がり情報の有無に対応したデジタル可変遅延素子選択と遅延時間の動的制御を行う方法「フラクショナル位相選択方法」を採用。これにより、従来の完全デジタル型CDRを約20倍上回るノイズ耐性を実現したという。