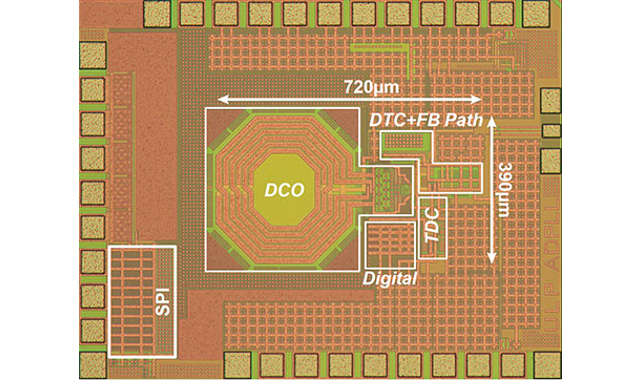

開発したPLLのチップ写真

東京工業大学は2019年2月19日、位相同期回路(PLL)の通常のサンプリング動作にサブサンプリング動作を組み合わせることで、極低消費電力で動作する分数分周タイプのデジタルPPLの開発に成功したと発表した。これまでは、サブサンプリング動作により低消費電力化が可能だが稀に誤った周波数を出力する問題があった。今回、動作時間の短い周波数同期回路を用いることで、この問題を解決した。

近年の高効率を目指すSoC(プロセッサやメモリなどのシステム実装に必要となるすべての回路が集積された集積回路)などのシステムにおいて、低消費電力CMOSの大規模集積回路(LSI)技術の重要性が高まっている。特にPLLは、通信分野のキャリア生成やプロセッサ、メモリなどへのシステムクロックの生成など多岐にわたり必須の回路で、性能を維持したまま低消費電力化する技術が不可欠だ。

PLLには整数分周型と分数分周型があり、整数分周型PLLでは基準信号に対して整数倍の周波数を出力するが、分数分周型では分数倍の任意の周波数の出力が可能だ。BLEなどの無線通信用には、整数分周型ではなく分数分周型のPLLが必要になる。分数分周タイプのデジタルPLLは、PLL自身の低消費電力化や小面積化などが期待されこれまで多くの研究がなされているが、500μW未満の低動作消費電力のものは開発されていなかった。

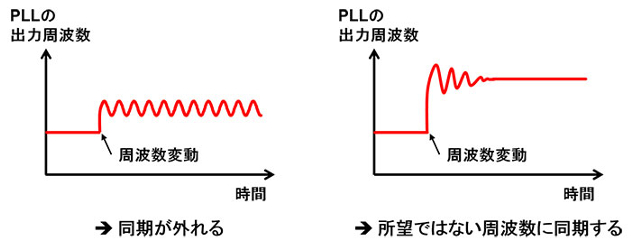

近年、PLLの低消費電力化、低ジッタ化(クロックの揺らぎを小さくすること)を図るサブサンプリング技術の応用も提案されている。しかし、ノイズなどによる出力周波数変動で、PLLが同期から外れる、出力周波数がリファレンス周波数の整数倍異なる周波数に同期するなど誤動作が生じやすい。誤動作は、周波数同期回路(FLL)をPLL内に実装することで、サブサンプリング動作中のPLLの周波数を常時モニターすることで回避できるが、FLLは常時動作しているためにPLLの消費電力が増大してしまう。

サブサンプリングPLLの誤動作の例

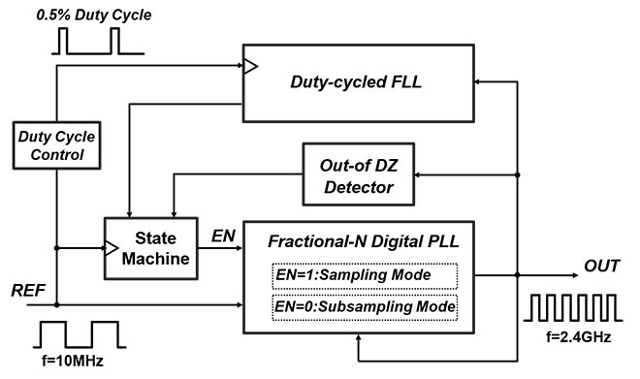

そこで東工大の研究グループは、サブサンプリング動作とサンプリング動作を組み合わせることで、低消費電力化とPLLの誤動作回避を両立したデジタルPPLを開発した。サンプリング動作時にPLLの周波数がリファレンス周波数に同期すると、PLLの動作モードは消費電力の少ないサブサンプリング動作に切り替わる。

サブサンプリング動作時の誤動作を解消するため、研究グループはPLLにODZ検出回路とFLLを実装。ODZ検出回路はPLLの同期が外れた状態を検出し、PLLの動作モードを自動的にサンプリング動作に切り替える。一方FLLは、PLLが所望ではない周波数に同期した状態を検出し、PLLの動作モードをサンプリングモードに切り替える。

通常のFLLは常にエネルギーを消費するため消費電力増大を招くが、研究グループはFLL内のカウンタの動作デューティ比(動作時間と待機時間の比で、低下させることで回路の消費電力が下がる)を0.5%にまで低下させるFLLの間欠動作を実装し、消費電力を削減した。加えて、通常のFLLを用いたサブサンプリングPLLと比較し、開発したPLLはサブサンプリング動作時の消費電力をおよそ70%削減できることをシミュレーションで確認した。

分数分周タイプのデジタル位相同期回路のブロック図

さらに、デジタルPLLの要素回路で、通常PLL全体の消費電力の大部分を占めるデジタル制御発振器(DCO)とデジタル時間変換器(DTC)の低消費電力化にも成功。PLL全体の動作時消費電力を減らした。

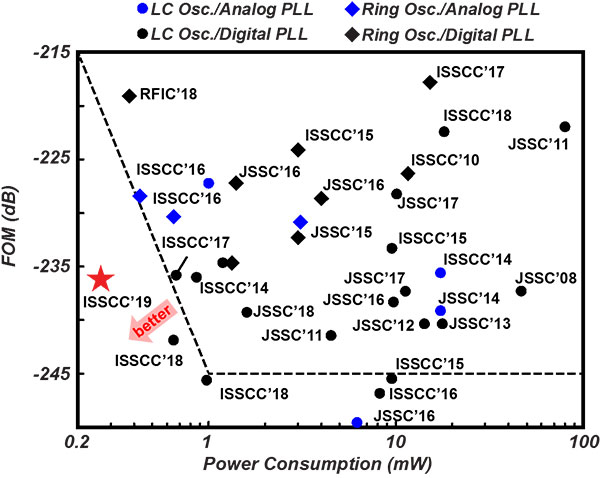

研究グループは今回考案した分数分周デジタルPLL回路を試作。試作したPLLは10MHzのリファレンス周波数から2.05~3.10GHzの出力周波数を生成した。動作時の消費電力は265μWで、これまでに報告されている分数分周デジタルPLLの中で最も低消費電力だ。また、クロック信号の立ち上がりや立ち下りのタイミングにおけるクロックの揺らぎの大きさを表すFoMは-236.8dBという良好な値を達成した。

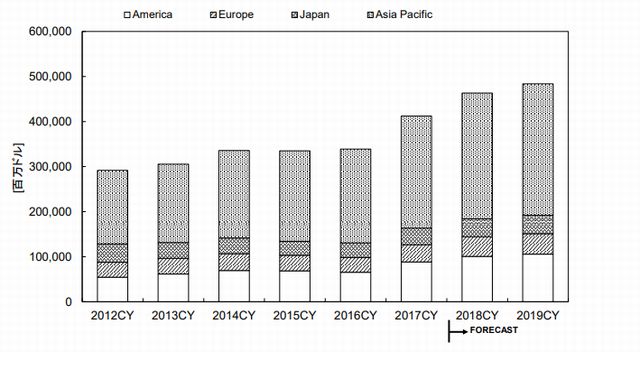

PLLのFoMと消費電力

今回開発したデジタルPLLは高いエネルギー効率を必要とするアプリケーションに活用できる。近年広がりを見せるIoT(モノのインターネット)機器は電池などの電源が必要で、いかに電池の寿命を延命し電池交換のメンテナンスコストを低下できるかが普及の鍵になっている。現在のIoT機器は通信時に最も電力を使い、その通信回路の中でもPLLは消費電力の大部分を占める。開発した超低消費電力PLLを適用することで、例えば現状3mW程度のレシーバの消費電力が約半分程度になるという。