- 2016-6-7

- ニュース, 製品ニュース

- CPU, CyberWorkBench, FPGA, IoT, NEC, 密結合プロセッサ, 異デバイス共通通信方式

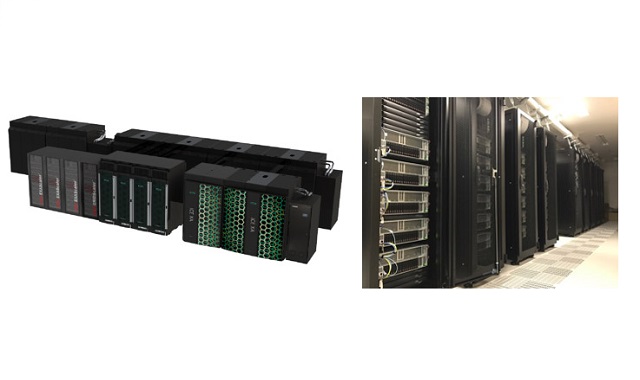

NECは2016年6月2日、CPU−FPGA密結合プロセッサを用いたIoT向けアプリケーションにおいて、CPUとFPGA間の高速通信を実現する「異デバイス共通通信方式」を発表した。

異デバイス共通通信方式は、CPU−FPGA密結合プロセッサにおけるCPUとFPGA間の広帯域な伝送路を活かした技術。FPGAにCPU上のデータをまとめて読み込ませたり、処理により異なる通信データサイズや要求性能に対応してデータの通信単位を調整したりすることにより、CPUとFPGA間の通信速度を高速化する。

異デバイス共通通信方式を使用すれば、処理に合わせて性能チューニングする手間を大幅に短縮できるようになる。また、異デバイス共通通信方式では、FPGAがCPU上のデータを直接読み書きするため、従来FPGAを利用するときに必要だったCPU上におけるソフトウェアの改変が不要になるという。

NECが同通信方式の性能をテストしたところ、同社の半導体設計ツール「CyberWorkBench」と併用することで、CPU−FPGA密結合プロセッサ上でのIoTの高精度分析処理の高速化に必要な設計時間を、約1/50に削減できたとしている。