- 2017-2-8

- ニュース, 製品ニュース, 電気・電子系

- CMOSイメージセンサ, ソニー

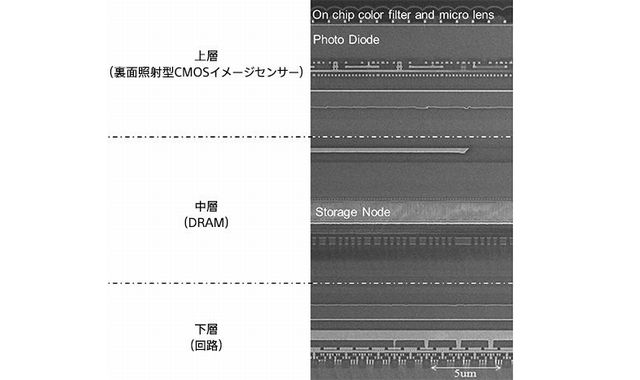

ソニーは2017年2月7日、DRAMを積層した3層構造の積層型CMOSイメージセンサを開発したと発表した。従来の裏面照射型画素部分と信号処理回路部分の2層構造の積層型CMOSイメージセンサに、DRAMを積層したもので、同社によると業界初となる。

同開発品は、高速で低消費電力の大容量DRAMを積層することで、1930万画素サイズの静止画1枚を、1/120秒(従来の約4倍)の高速度で読み出せる。高速で読み出すことで画素の行ごとの読み出し時間のズレを抑えられるため、露光時間を制御するメカニカルシャッターがないスマートフォンでの撮影でも、CMOSセンサ特有のフォーカルプレーン歪みが抑えられる。

また、高速で読み出せるようになったことで、フルHD(1920×1080画素)サイズで従来の約8倍となる毎秒最大1000フレームでのスーパースローモーション動画の撮影が可能になった。DRAMに蓄積した高速撮影データをイメージセンサから出力し、外付けのISP(画像処理回路)で信号処理することで、通常速度動画とスローモーション動画をシームレスにつないだ臨場感のある動画を、スマートフォンでも撮影できるようになる。

さらに、高速に読み出した信号を一旦DRAMに保存することで、イメージセンサから他のLSIに出力する際の規格に合わせた速度で出力できる。また、画素部分から読み出したアナログ信号をデジタル信号へ変換する回路を、従来の2段から4段構造に倍増することで処理能力向上が図られている。