- 2020-2-12

- ニュース, 技術ニュース, 電気・電子系

- 5nm FinFET CMOS, PLL, ソシオネクスト, 分数分周型クロック回路, 東京工業大学, 研究

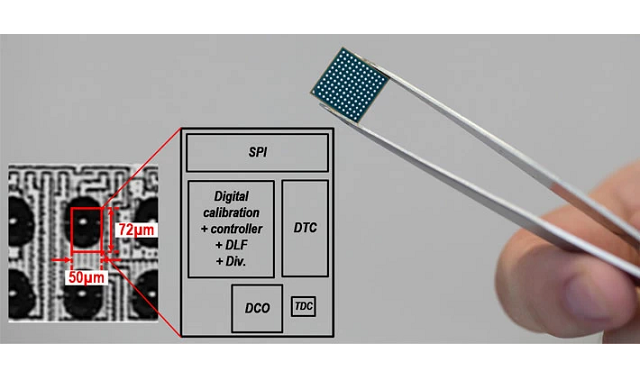

開発した分数分周型クロック回路を搭載したチップ写真(回路面積は0.0036mm2)

東京工業大学は2020年2月10日、ソシオネクストと共同で、PLLのデジタル化によって最先端の5nm FinFET CMOSプロセスで世界最小クラスの高性能分数分周型クロック回路の開発に成功したと発表した。

LSIには、回路内で必要になる周波数などのクロック回路が搭載されている。従来から、LSIに搭載されるクロック回路はPLL方式のものが用いられているが、アナログ回路であるPLLは、FinFETなどの最先端の半導体製造プロセスを適用する場合に設計が難しく、またデジタル回路と比較して回路面積が大きくなるという課題があった。また、以前よりデジタル型のPLLの検討が行われていたが、一部にアナログ回路が含まれており対象部分の手作業による設計が必要だった。

今回の研究開発では、デジタルPLLにおいて従来アナログ回路で構成されていたデジタル制御発振機および時間差デジタル変換器をデジタル回路により構成。これによりPLL回路全体をデジタル回路として構成できた。その結果デジタル回路開発で使用されている回路構成やタイミング設計、自動配置配線ツールを用いたPLLの自動設計ができ、製造プロセスの微細化に合わせてスケーラブルに回路面積を小型化できる。

開発したクロック回路は小型で、なおかつクロック数の安定性を表す優れたジッタ特性を持つ。さらに細かい周波数調整ができる分数分周型PLLで構成されており、周辺への電磁妨害を抑制できるスペクトル拡散クロックの生成ができる。

今回の成果である高性能クロック回路により、世界最先端の5nmプロセスによる高性能/低消費電力/小面積のSoC(System on Chip)を短期間で設計することが可能になった。また、クロック回路のデジタル化により、高効率なデジタル設計ツールの活用ができ、将来のSoCの全自動設計への道が拓かれた。