- 2025-2-5

- 半導体, 技術ニュース, 海外ニュース, 電気・電子系

- 3次元(3D)半導体チップ, AI, AIハードウェア, サムスン高等技術院(SAIT), シリコン貫通電極(TSV), マサチューセッツ工科大学(MIT), モノリシック3D集積化技術, 単結晶半導体, 学術, 論理回路, 遷移金属ジカルコゲナイド(TMD), 高積層化技術

Credit: Cube 3D Graphic

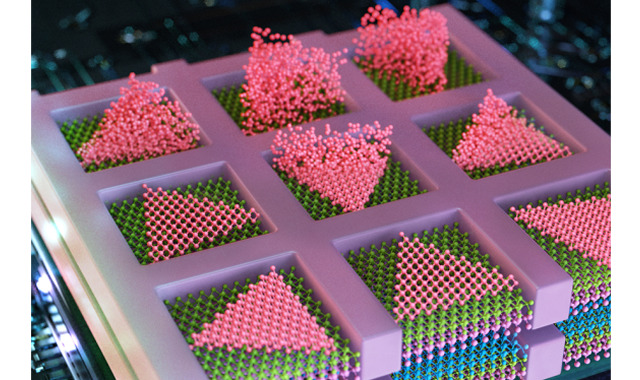

米マサチューセッツ工科大学(MIT)とサムスン高等技術院(SAIT)らの共同研究チームが、3次元(3D)半導体チップの高積層化技術を開発した。同技術は、チップ上のトランジスタ数を飛躍的に増加させ、より効率的なAIハードウェアの作製を可能にするという。同研究成果は2024年12月18日、『Nature』誌に掲載された。

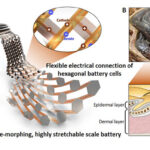

半導体チップの集積化技術では、従来の2次元平面上での微細化が限界に近づきつつあり、3D積層化による高集積化技術が注目されている。高集積化に加え、データ転送経路の短縮や動作速度の向上、消費電力の低減という利点を付与できるため、大容量メモリーやプロセッサなどの幅広い分野で期待されている。

従来の3D積層化技術は、シリコン製半導体チップの内部を垂直に貫通する、シリコン貫通電極(TSV)を採用している。しかし、TSV技術には、コストのかかる穴あけ工程とチップの位置ずれなど、いくつかの課題があった。

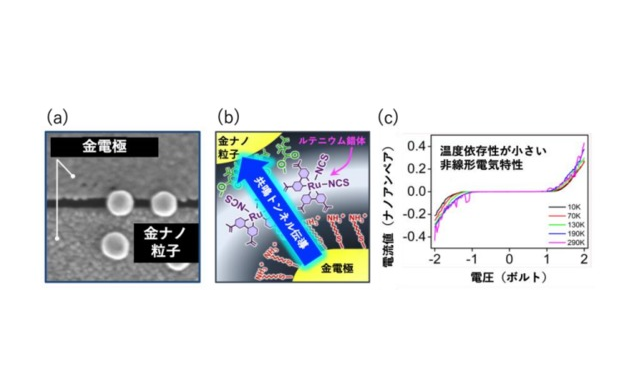

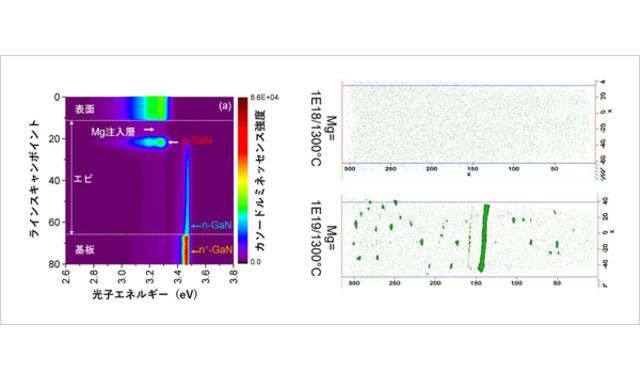

研究チームは同課題を克服するため、シリコン層を介さずに単結晶半導体をシームレスに接続するモノリシック3D集積化技術を使用し、遷移金属ジカルコゲナイド(TMD)に適用した。2次元材料のTMDは小型で高性能なトランジスタ(FET)を製造可能で、シリコンの後継材料として有望視されている。

研究チームは、回路を形成済みのチップ上に、回路に影響を及ぼさない380℃という低温で単結晶TMDを成長させることに成功した。さらに、2つの異なるTMD(n型FET材料の二硫化モリブデンとp型FET材料の二セレン化タングステン)を交互に積層した多層チップを作製した。同作製法は、複数の半導体層を直接接触でき、チップの半導体素子の密度を2倍にしつつ、層間の通信や計算をより高速にできるという。

研究チームは、同作製法をAIハードウェアに利用することを視野に入れている。将来、ノートパソコンやウェアラブルデバイス用の積層チップが、現在のスーパーコンピューターと同等の速度とパワーを持ち、物理的なデータセンターと同等の膨大な量のデータを保存できるようになることを期待している。

MITのJeehwan Kim准教授は「このブレークスルーは、半導体業界に大きな可能性を拓き、従来の制限なしにチップを積層させ、AIや論理回路、メモリーへの応用において、桁違いの計算能力向上につながる可能性があります」と説明した。