- 2016-2-5

- ニュース, 海外ニュース, 製品ニュース

- 2D Compression, Cadence Design Systems, Elastic Compression, GLOBALFOUNDRIES, Microsemi, Modus Test Solution, Sequans Communications, SoC, Texas Instruments

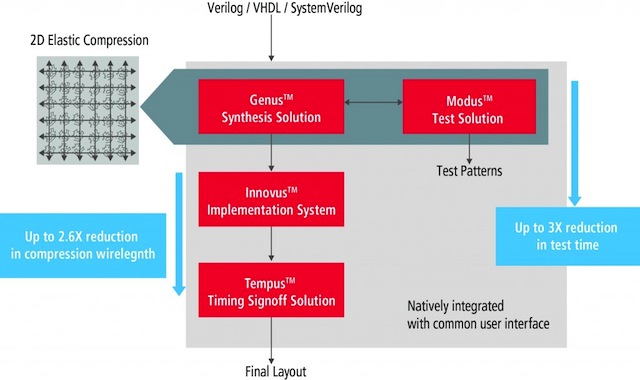

米Cadence Design Systemsは2016年2月3日、SoCのテスト時間を最短で1/3に短縮できるテスト設計ツール「Modus Test Solution」を発表した。フィジカルアウェアな2D Elastic Compressionアーキテクチャを搭載した同テストツールは、デザインサイズや配線に影響を与えずに圧縮率400倍超を実現するという。

Modus Test Solutionは主に、設計テストに伴う課題に対処するための機能として、「2D Compression」「Elastic Compression」「組み込みメモリーバスのサポート」「強力なスクリプト記述とデバッグの共通環境」を備えている。

2D Compression

スキャン圧縮ロジックが、チップのフロアプラン全体にフィジカルアウェアな2次元のグリッドを形成し、配線長を縮減するとともに高い圧縮率を実現。圧縮率を100倍とした場合、2D Compressionは既存のスキャン圧縮アーキテクチャと比べて配線長を最大60%短縮できる。

Elastic Compression

デコンプレッションロジックに埋め込まれたレジスターにより、ATPG (automatic test pattern generation)実行中に、複数スキャンサイクルをまたいだケアビットの制御が可能。これにより、400倍を超える圧縮率でも高い故障検出率を維持する。

組み込みメモリーバスのサポート

IPコア内蔵メモリーのプログラマブルメモリー・ビルトイン・セルフテスト(PMBIST)の高速実行時に、シェアド・テストアクセスバスを挿入することが可能。この機能は、自動車の安全性アプリケーション用ソフトのプログラマブルなテストアルゴリズムやFinFET SRAMも包含する。

強力なスクリプト記述とデバッグの共通環境

DFT (Design for test)ロジックの挿入および、Genus Synthesis Solution、Innovus Implementation System、Tempus Timing Signoff Solutionで共用される、新しく統合されたTCLスクリプト記述およびデバッグ環境を用いるATPG機能。

Modus Test Solutionは、「米GLOBALFOUNDRIES」「米Texas Instruments」「米Microsemi」「仏Sequans Communications」の4社が発表に先駆けて利用。GLOBALFOUNDRIESはテスト時間を70%削減、TIはテスト時間を40%削減、Microsemiは配線長を60%、スキャン時間を50%削減、Sequansはテスト時間を50%削減したという。