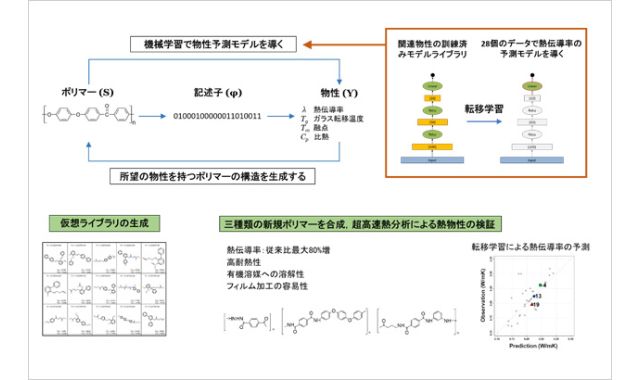

全結合半導体アニーリングLSIチップ

東京理科大学は2020年1月23日、全結合型半導体アニーリング方式を搭載した人工知能集積回路(AIチップ)を開発したことを発表した。組み合わせ最適化問題の求解用に開発し、512個の全結合型スピンを新しいチップアーキテクチャによって搭載した。

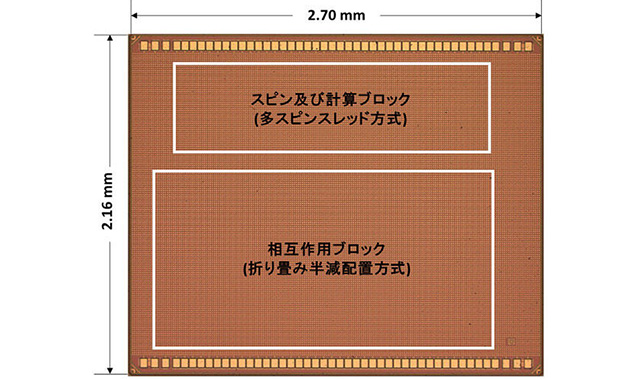

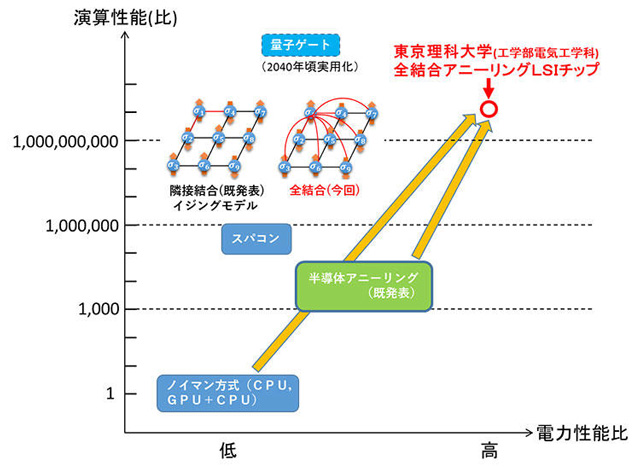

これまでの研究では、隣り合うスピン同士にのみ相互作用があると仮定し、スピンの結合をイジングモデルで考える「隣接結合」と呼ばれる方式を主に用いていたが、研究グループは、スピン同士のすべてを結合させる全結合方式のAIチップを開発。LSIに世界で初めて実装したという。チップ面積は、28nmのCMOS半導体プロセスで2.16×2.70mmとなっている。512個のスピンを搭載し、1秒以下で22都市の巡回セールスマン問題を解ける。

組み合わせ最適化問題求解性能比較

全結合方式の利点として、幅広い問題を少ないスピン数で解けることが知られているが、LSIチップ化するためには、配線層数の制限から、すべてのスピンの結合を実装できる方法の開発が難しいという課題があった。しかし、新しいチップアーキテクチャにより、512個の全結合型スピンを搭載できるようになったという。

今回開発した主要な技術には、分離アレー型全結合方式、多スピンスレッド方式、折り畳み半減結合セル配置方式がある。

分離アレー型全結合方式では、新しいチップアーキテクチャとして、結合セルを2次元アレー上に配置し、これと分離してスピンセルを1次元的に配置した。全結合方式のため、スピンセル数は隣接方式スピンセル数の平方根の値に減少する。また、結合セル数も数分の一となっている。

多スピンスレッド方式は、今回のチップでは8スピンスレッドを搭載しており、外部からスピンセル部分と2次元アレーの結合セル部分へのデータの出し入れが1回でも、8回分の計算が一度にできる。今回、1次元のスピンセル部分と2次元アレーの結合セル部分を分離したことにより、スピンセル部分を複数個設ければ、複数回数または複数チップ分の動作を一度にできる。この複数の1次元スピンセル配列を多スピンスレッドと名付けた。

折り畳み半減結合セル配置方式では、評価ボードも開発し、実証実験した結果、8スピンスレッドが同時に室温で動作することを確認した。一回の動作で、8チップ分の結果を取り出せたという。今回の全結合方式では、結合セルを2次元アレーとするチップアーキテクチャとしたが、結合セル数を半減。単純な2次元アレーの配置のままでは、2つのセルを入れ替えた場合の結合セルを別個のものとして取り扱うだけでなく、自分自身との結合も入ってしまうため、これらを取り除いた。

しかし、2次元アレーをLSI上にそのまま配置すると、レイアウトが三角形になることから、三角形の一部を切り取り、折り畳むように移動させることで結合セルアレー全体のレイアウトを矩形にして、結合セル部の面積を削減した。28nmのCMOS半導体プロセス技術を用い、これらをLSIチップ化したという。

これまでの隣接結合方式では、今回の全結合型512スピンを実現するためにおよそ26万個のスピンが必要となる。さらに、この26万個のスピン各々に対して、隣接結合ながら4~8個の結合回路が必要となり、実装面積が増大するだけでなく、オーバーヘッド時間も大きくなる。

また、22都市の巡回セールスマン問題は、スピン数512個だと1秒以下で解くことができるが、従来のノイマン型の高性能CPUでは1200年かかるという。隣接結合型半導体アニーリング方式のAIチップでは、最大16都市に相当する問題を解くことが限界となっている。

今回の技術を応用すると、小型、低電力で高性能なシステムを運用できる。東京理科大学は今後、IP(知的財産)として開発したLSIの高位記述を提供し、企業などとの実証実験へつなげることを探っていくとしている。