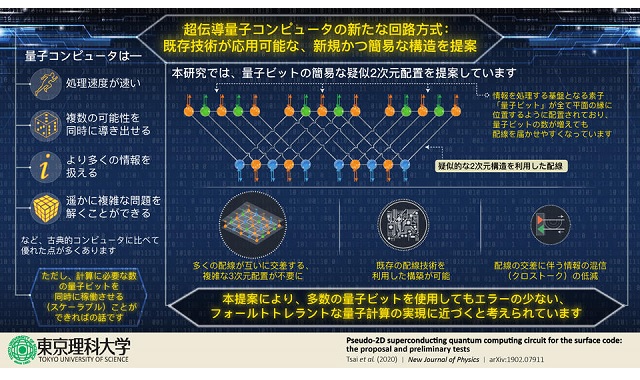

東京理科大学は2020年4月23日、理学部第一部物理学科教授の蔡兆申氏が、現在のコンピュータよりはるかに高速、省エネルギーな計算力に期待のかかる量子コンピュータについて、計算に使用する量子ビットの新たな回路方式を提示したと発表した。

量子コンピュータの論理的な能力を向上させるためには、より多くの量子ビットが必要だが、量子ビットの数が増えればその分、回路上で必要な配線も増え、特にチップの中心に位置する量子ビットには配線が届きにくくなるといった配線問題が存在する。この配線問題を解決するために、量子ビットに対して3次元(垂直)配線の研究が進められているが、技術的に非常に難しいという。

蔡氏は1999年に超伝導量子ビットを開発した。しかし、この超伝導量子ビットが持つ量子の状態は、観測の影響だけでなく、量子ビットの周囲の環境などによっても影響をうけるため、量子ビットは古典的なビットと比べてエラーが起こりやすく、また多数の量子ビットを同時に稼働させることも難しい。

そこで蔡氏らは、エラーが少なく、必要な計算に合わせて必要な数の量子ビットを稼働させられる量子コンピュータの開発に向け、多数の量子ビットを実装するための回路方式に着目した研究を進め、3次元の配線技術を必要とせず、完全に平面的な配置を維持できるような回路方式を開発した。

蔡氏が新開発した回路方式は、量子ビットを2次元に配置したまま、全ての量子ビットへの配線も平面に配置するものだ。量子ビットの正方格子を、それぞれの並びごとに、巧妙に折り畳む工夫がなされている。そのため、量子ビットが2列に並んだ(bi-linear array)新たな配置が取れる。この形状により、2次元配置を崩さないまま、全ての量子ビットを縁に出して簡易な平面配線を実現できる。この回路方式を使えば、配線間の混信や、損失が低減され、複数の量子ビットのエラーが抑えられ、論理量子ビットの信頼性の向上につながることが期待できる。

なお、2列に並んだ形であっても、元の隣り合う量子ビットのつながり方は維持する必要があり、そのために一部の量子ビットをつなぐ配線に交差が生じる。これは局所的な立体構造を使用することで実現できる。研究では、このような立体構造の寄与を調べ、回路方式を評価したところ、現状の技術を用いても十分に実現可能な回路であることが実証された。

本技術は、3次元配列を一切使わなくても、既存の2次元配列技術を応用し、量子コンピュータの実装が平面回路だけで行える将来への道筋を示している。