- 2022-12-8

- 制御・IT系, 技術ニュース

- FPGA, Pコンピューター, カリフォルニア大学, カーボンニュートラル, スピントロニクスPコンピューター, スピントロニクス素子, メッシーナ大学, 東北大学, 研究, 確率動作スピン素子, 確率的アルゴリズム, 確率論的コンピューター, 磁気抵抗メモリ, 量子コンピューター

東北大学は2022年12月7日、米カリフォルニア大学、伊メッシーナ大学と共同で、機械学習や組合せ最適化などの用途で威力を発揮する確率論的(「P」)コンピューターを開発したと発表した。古典コンピューターで確率的な演算をする場合に比べ、演算性能が約5桁高く、消費電力が約1桁低いことを明らかにした。

人工知能(AI)やデジタルトランスフォーメーション(DX)の進展に伴い、コンピューターに要求される演算性能がこれまでに経験したことがないペースで増大している。一方で、地球温暖化ガスの排出を抑制し、2050年カーボンニュートラルを達成するため、コンピューターの省電力化もまた重要な課題になっている。

演算性能の向上と省電力化は、相反する関係にあり、従来型(古典)コンピューターですべて対応するのは難しく、古典コンピューターが苦手とする問題に特化した新概念コンピューターの研究開発が活発に進められている。量子コンピューターは、その一例で、量子力学的性質の取り扱いが本質的に重要となる問題などを効率的に処理できると期待されている。

今回の研究対象「確率論的コンピューター(Pコンピューター)」 も、特定の用途で威力を発揮すると期待される新概念コンピューターの一つで、Pコンピューターは、時々刻々と0と1を確率的に出力 し、情報を表現する「確率ビット:Pビット」で構成される。

古典コンピューターが苦手とする問題の典型例には、組合せ最適化問題、サンプリング、機械学習などがあり、これらの問題を扱う際に確率的なアルゴリズムがしばしば用いられる。しかし、情報を0と1で決定論的に表現して逐次的に処理する古典コンピューターとは本質的に相性が悪く、多くの電力を費やすという課題がある。

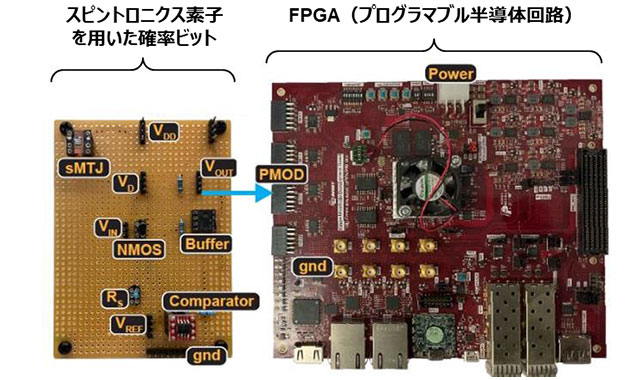

研究チームは今回、確率動作するスピントロニクス素子と、プログラムできる半導体回路(FPGA)を組み合わせ、規模が先行研究から大幅に拡大されたPコンピューターを開発。組合せ最適化問題のアルゴリズムを用いて、52,193,789=6,883×7,583をはじめとする、以前の研究を5桁上回るさまざまな整数の因数分解に成功した。

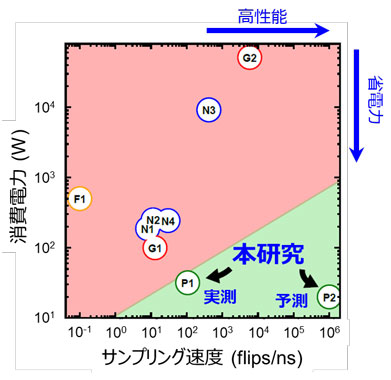

加えて、実験で測定された性能を基に、確率的なアルゴリズムを古典コンピューター上で実行して計算する場合と比べ、演算性能が約5桁、消費電力が約1桁低減するポテンシャルがあることがわかった。

今回の研究は、大規模な演算ができるFPGAと、確率動作スピントロニクス素子からなる高性能Pビットを組み合わせたことがポイントになる。疑似的に最大7,085個のPビットをFPGA上に実装でき、これを自然な熱で電力を消費することなく状態が更新されるスピントロニクスPビットで駆動し、高度な計算をする。

次に、スピントロニクス素子を用いたPコンピューターの演算性能と、消費電力を測定。古典コンピューターで確率的なアルゴリズムを用いて演算する場合と比べた。その結果、FPGAを用いたPコンピューターは実測値ベース(106.28flips/ns、32.72W)で、既に古典コンピューターの典型値と比べて、消費電力が3分の1から10分の1程度低く、演算性能が2倍から10倍程度高かった。

加えて、東北大学のグループは以前、超高速で熱による状態更新ができるスピントロニクス素子を開発している。また、同様なスピントロニクス素子は、磁気抵抗メモリ(Magnetoresistive Random Access Memory)で既にメガビット以上の規模で量産されている。

これらの技術を適用した専用集積回路の作製時に予測される値は、1,000,000flips/ns、20W。実測値から演算性能は、さらに4桁向上し、消費電力はさらに約40%低減する。古典コンピューターの典型値と比べると、演算性能で約5桁、消費電力で約1桁凌駕する特性が得られる。

スピントロニクス確率論的コンピューターと、古典コンピューターで確率的アルゴリズムを実行した場合の計算性能(サンプリング速度:横軸)と消費電力(縦軸)の比較

今回の研究により、基本動作の確認に留まっていたスピントロニクスPコンピューターが、確率的に取り扱うことで効率的に求解できる問題に対して、古典コンピューターと比べ、圧倒的に優れた計算性能と電力効率を示すことが明らかになった。今後、この技術を発展させていくことにより、超高性能で省電力のコンピューターが実現される確率が高まっていくと期待される。