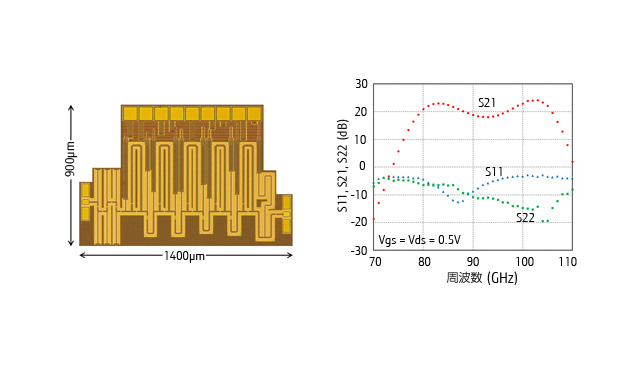

55-nm DDC CMOSプロセスを用いた0.5V動作W帯増幅回路のチップ写真(左)と、0.5V動作W帯増幅回路の実測結果(右)

三重富士通セミコンダクター(MIFS)と広島大学は2017年6月5日、MIFSのDeeply Depleted Channel(DDC)技術を用いて、80〜106GHzの広帯域にわたって動作する超低消費電力CMOS増幅器を開発したと発表した。

MIFSのDDCは、0.5V以下の電源電圧(VDD)で動作する超低消費電力トランジスタの製造を可能にする技術。プレーナー型CMOS構造のチャネル部分に不純物濃度の異なる複数の層を形成することで、不純物によるしきい値ばらつきの影響を低減し、性能低下を最小限に抑えながら低いVDDでの動作を可能にする。

一方、広島大学ではこれまで、デバイスの最大動作周波数近くで動作するテラヘルツ無線回路を研究してきた。この高性能化技術を応用し、DDC技術を組み合わせることで、CMOSとしては世界で初めてVDD=0.5Vで動作する80〜106GHzのミリ波帯用増幅器を開発した。また、最先端のプロセスに比べ耐圧の高い55nmテクノロジーで低電圧動作させることにより、低消費電力と信頼性を達成している。

近年、5G(第5世代移動通信システム)や車載レーダー向けに、ミリ波ビームを電子的にスキャンするフェーズドアレイシステムが注目されている。このシステムでは1つの送受信システムの中に数十から数百個の送受信回路を要するため、送受信回路の消費電力削減が課題となる。今回の開発はこうした課題に対応するものだ。