3次元積層プロセス技術の概要

産業技術総合研究所(産総研)の研究グループは、内閣府が主導する革新的研究開発推進プログラムの研究の一環として、次世代の不揮発性メモリーである磁気ランダムアクセスメモリー(MRAM)の3次元積層プロセス技術を開発した。産総研などが2017年5月16日に発表した。

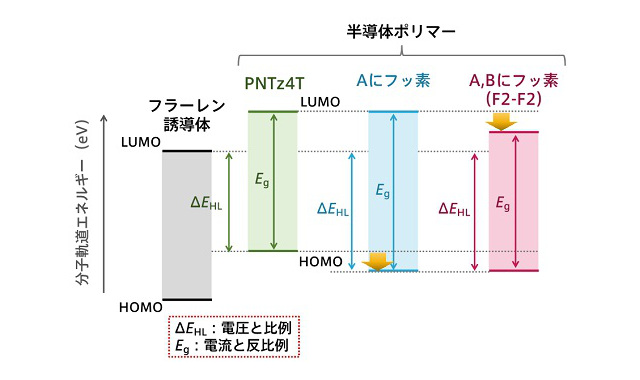

MRAMは不揮発性、高速、高書き換え耐性などの特徴を持ち、新世代ユニバーサルメモリーとして注目されている。垂直磁化TMR素子をベースとする記録ビットと、ビット選択に用いる半導体トランジスタ(CMOS)、金属配線(通常、多結晶の銅配線)からなり、通常、垂直磁化TMR素子薄膜(TMR薄膜)は、CMOS形成後に金属配線上に直接形成される(逐次積層)。

産総研は、大容量MRAMを実現するための中核技術の研究開発を行ってきており、現在、単結晶TMR薄膜を用いたMRAMの製造プロセス実現に取り組んでいる。このプロセスが実現すれば、原子レベルでの薄膜平坦性や、薄膜均質化による性能バラツキ抑制、さらに多結晶材料にはない高性能な新材料の利用などが可能になる。単結晶TMR薄膜のCMOS上への積層は、TMR薄膜を別途単結晶シリコンウエハー上に形成し、後でCMOSウエハーと統合するという「3次元積層プロセス」を活用することで可能となる。

しかし、TMR薄膜ウエハーとCMOSウエハーのような全く異なる動作原理を持つデバイスを形成したウエハーによるnmスケール厚さの薄膜同士の積層技術は十分に確立されていない。また、TMR素子には厚さわずか1nmと極めて薄く機械的強度が弱いMgOトンネル絶縁層が含まれているため、さまざまな機械的ダメージが素子に直接加わる3次元積層プロセスのTMR素子への応用は難しいと考えられていた。そこで今回産総研では、単結晶TMR薄膜よりもさらに機械的強度の脆弱な多結晶TMR薄膜を用い、低ダメージなMRAM製造用3次元積層プロセス技術開発に取り組むこととした。

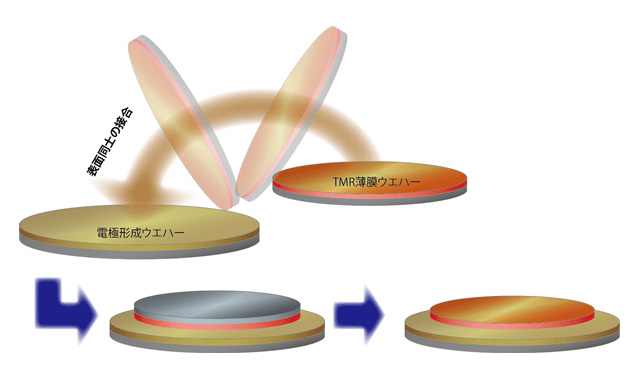

今回開発した3次元積層プロセス技術は、直径150mmのシリコンウエハー上に、単結晶TMR薄膜よりも機械的強度の弱い多結晶TMR薄膜層を形成したウエハー試料と、直径200mmのシリコンウエハー上に銅電極層を形成したウエハー試料を別々に作製。高真空中で両ウエハーの背面から荷重をかけ、タンタル接合層の表面同士を接合面として両ウエハーを接合する。その後、多結晶TMR薄膜層のウエハーを裏面から研削して除去し、直径200mmシリコンウエハー上に、銅電極層、タンタル接合層、多結晶TMR薄膜層の順に形成された3次元積層試料を得た。

タンタルの表面平坦性や活性化条件の適正化のしやすさに着眼したこの積層技術により、厚さがnmスケールの接合層同士である高品位のダイレクト接合を実現した。同時に、懸念されたウエハー接合後のMgOトンネル絶縁層中での破壊は回避できた。

さらに、今回の3次元積層プロセスにより形成された3次元積層試料に微細加工を行い、サイズが28nmから65nmのMRAMデバイスを作製して動作を確認したところ、3次元積層プロセスを経た後のMRAMデバイスは、読出性能/書込性能は全く劣化せず、STT-MRAMで重要な性能指標となる「データ書き込み効率」は2に達した。これは、世界トップクラスの性能であるという。さまざまなダメージ要因はMRAM動作には全く影響していなかった。

今回の多結晶TMR薄膜よりも単結晶TMR薄膜の方が機械的強度が強いので、今回の3次元積層プロセスは単結晶TRM薄膜にもそのまま適用できると考えられる。これが実現すれば、単結晶TRM薄膜の特徴である、原子レベルでの薄膜平坦性や薄膜均質化による性能バラツキの排除、高性能な単結晶材料の使用などのメリットが得られると考えられる。

産総研では現在、単結晶TMR薄膜の開発を進めており、今後2年以内に単結晶TMR薄膜とCMOSウエハーの3次元積層プロセスを確立し、5年以内に3次元積層MRAMの製品開発の着手を目指す。