東京工業大学は2020年6月22日、ステルスダイシングを用いたウエハーにダメージを与えず、かつ無駄なくチップ加工できる極薄ウエハー加工技術を開発したと発表した。ステルスダイシングは、パルスレーザーをウエハー内部に集光し、制御した亀裂を生成することによってウエハーを分割する手法である。

CPUやメモリーなどの半導体は微細化によって性能を向上させてきたが、従来の2次元微細化技術は物理的な限界が迫っている。その限界を突破するために、ウエハーをミクロンレベルにまで薄くし、シリコンウエハーを貫通させて埋め込み配線で上下チップを接続させる、TSV配線を用いた3次元積層の開発が進められている。

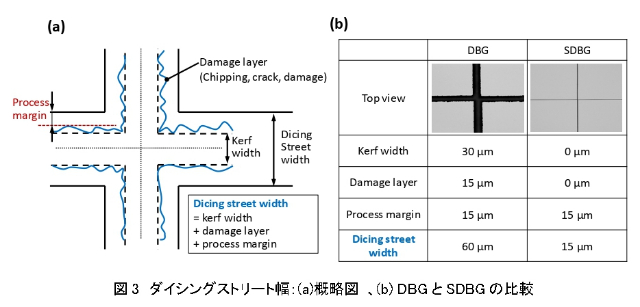

しかし、ウエハーを元の厚さから10分の1以下に薄くしてダイシング(分割)すると、チッピングと呼ばれる欠けが増加する。またダイシングストリート幅によってウエハーあたりのチップ数が決まるため、チッピングがなく、ダイシングストリート幅ができるだけ狭いダイシング方法が必要とされ、ステルスダイシング技術がすでに実用化されていた。

今回の研究では、デバイス面に生じるわずかなダメージの評価方法を確立すること、そしてステルスダイシングにおけるレーザー波長と照射方法を工夫することにより、ダイシングストリート幅を従来技術よりも縮小することを目指した。

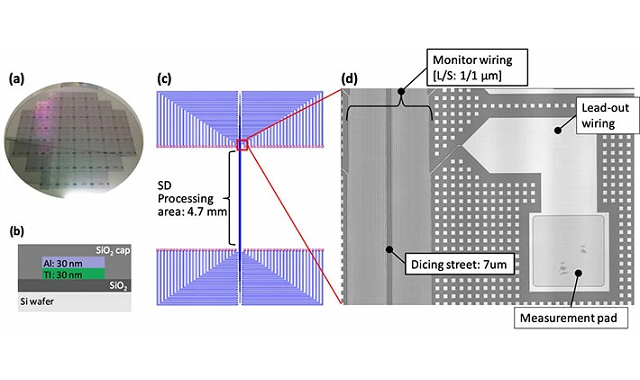

まずダメージ検出のための評価用チップとして、配線長/スペースが1µm/1µm(Al/Ti)のTEGウエハーを開発した。薄化ウエハー用のステルスダイシングプロセスの一種「SDBG」プロセスを想定して、ウエハー厚50µmとしたときのダメージ評価を実施したところ、波長1099nmのレーザー使用時にダメージが発生しないことを確認。波長1099nmのレーザーによってダメージを発生させないステルスダイシングが可能であることを明らかにした。さらにその際に必要なダイシングストリート幅を、従来のダイシング方法である「DBG」と比較した結果、従来は60μmであったものが約4分の1の15μmで済むことが分かった。

今回の開発によるダイシングストリート幅の縮小はチップ収率を向上させ、ウエハー製造プロセスを効率化することが期待されるという。今後は今回開発した技術の実用化に向けて、波長1099nmレーザー専用の光学エンジンの製品化を目指す。