- 2020-11-13

- 制御・IT系, 技術ニュース

- NII, NISQ, Noisy Intermediate-Scale Quantum, NTT, コンパイラ設計, 国立情報学研究所, 日本電信電話, 研究, 誤り耐性, 量子コンピュータ, 量子計算

国立情報学研究所(NII)と日本電信電話(NTT)は2020年11月12日、大規模な量子コンピュータ上の計算回路の圧縮化とコンパイラ設計のための新しいアプローチを定式化したと発表した。大規模量子コンピュータに必要な量子ビット数の大幅削減と、計算時間の短縮化による量子コンピュータの高速化が期待される。

量子コンピュータは、量子コンピュータ中のデータにエラーがあることからNISQ(Noisy Intermediate-Scale Quantum)マシンとも呼ばれている。エラーの影響が大きく、十分に実用上量子優位性を発揮するために、量子ビット操作上のエラーに対して耐性を持つ大規模量子コンピュータの出現が待たれている。

このような大規模な量子コンピュータは、誤り耐性型汎用量子コンピュータとも呼ばれており、誤りに耐性を持つ符号化の構造を持つことが特徴。だが、大きな課題の一つとして、誤りに耐性を持つ符号へのコンパイルや最適化の手法の開発が挙げられていた。

量子コンピュータの設計に最も多用されている誤り耐性のある符号化はトポロジカル符号で、中でも特に代表的なものは、超伝導量子ビット実装の2次元表面符号と、主に分散型の量子コンピュータの設計に用いられる3次元トロポジカル符号となる。

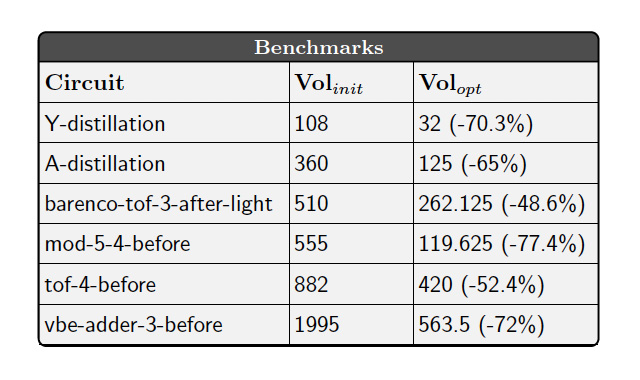

研究では、これらのトポロジカル符号を統合化し、量子計算回路の最適化を通して、量子コンピュータの誤り耐性実装に伴う大規模なオーバヘッドの低減と、コンパイラ設計の中心となる量子コンピュータ言語への新しいアプローチを提案。量子計算サブルーチン回路を平均約70%圧縮でき、大規模量子コンピュータの開発に必要とされるリソースを低減できたという。

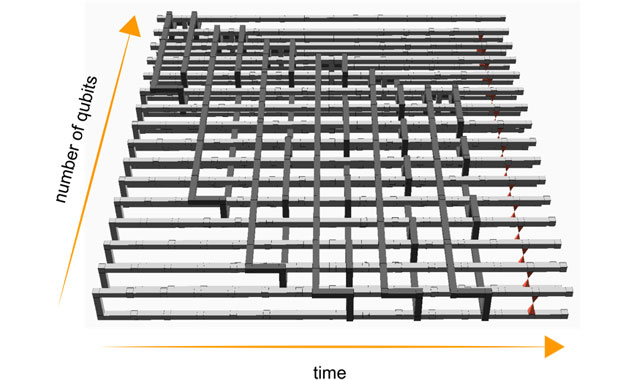

まず研究では、3次元トポロジカル符号上の量子計算回路にZXカリキュラスを応用。ZXカリキュラスのもつ演算機能を用い、量子計算回路を圧縮化した。3次元トポロジカル符号では、論理量子ビットを定義するために挿入されたディフェクトと呼ばれる構造が絡み合うことでトポロジーを変え、演算を実装するために、量子計算回路を絡み合うパイプ構造として3次元的に視覚化できる。量子計算回路の圧縮化は、このパイプ構造がつくる体積を圧縮することで達成される。

研究では、この手法をよく使われる量子回路のサブルーチンに対して用いて、平均約70%の圧縮率を達成した。量子計算回路を圧縮した分、量子コンピュータに必要とされる量子ビット数を削減すると同時に量子計算回路の実行時間も短縮化し、量子計算を高速化する。

また、研究では、ZXカリキュラスと3次元トポロジカル符号間の関係性を明らかにし、定説化。ZXカリキュラスに注目し、これまで別に発展してきた2次元表面符号と3次元トポロジカル符号を統一的に扱い、ZXカリキュラスの量子コンピュータ言語としての可能性を示した。これまでの定説を覆し、3次元トポロジカル符号で高い回路圧縮ができるという。さらに2つの符号のハイブリッドもでき、これまでの方法に比べてより高効率に量子計算回路を圧縮する。

この手法は、誤り耐性の実装に必要とされるリソース負荷を低減することにより、より早い大規模量子コンピュータの実現が期待できる。また、大規模量子コンピュータを設計する上で、量子コンピュータアーキテクチャと合わせて中心的な位置を占め、命令制御アーキテクチャやコンパイラの設計の基礎としての役割を担っていくことが期待される。