- 2017-6-2

- 製品ニュース, 電気・電子系

- LDMOS, アナログパワー半導体, 人体帯電モデル, 完全分離型Nチャネル, 東芝

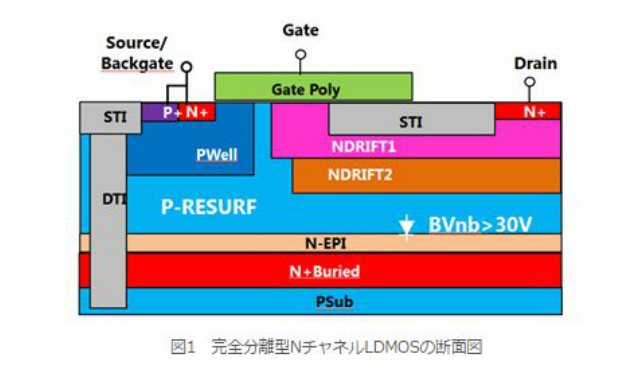

東芝は2017年6月1日、0.13μm(マイクロメートル)世代のアナログパワー半導体向けに、高い人体帯電モデル(HBM)耐量と負電圧耐性を両立した完全分離型Nチャネル-LDMOSの素子を開発したと発表した。

近年、車載アナログICやパワーICの分野において、高い負電圧にも耐えられる完全分離型Nチャネル-LDMOSの開発が進んでおり、特に40Vを超えるような高い電圧にも対応する素子の需要が増加している。しかし、半導体製品に求められるHBM耐量と負電圧耐性の両指標を同時に高い値にするためには素子のサイズを大きくする必要があり、小型化や製造コストの抑制が課題となっていた。

今回の開発では、デバイス特性のシミュレーションで多様な指標を検証し、ドレイン直下の電界強度(EUD)がHBM耐量に依存することを見出した。また、EUDを用いて素子構造と半導体材料の濃度を調整して素子特性を最適化し、HBM耐量と負電圧耐性を改善した。この指標を用いて25Vから96Vまでの完全分離型Nチャネル-LDMOSを開発したが、中でも80V耐圧系ではHBM耐量の基準であるHBM±4kVを満たす完全分離型Nチャネル-LDMOSのサイズを、最適化前と比較して46%縮小したという。

東芝は、同社の0.13μm世代のアナログパワー半導体プロセスのひとつ「BiCD-0.13G3プロセス」に今回開発した技術を適用して車載アナログ半導体を試作し、2018年から量産する予定だ。