- 2017-9-14

- ニュース, 製品ニュース, 電気・電子系

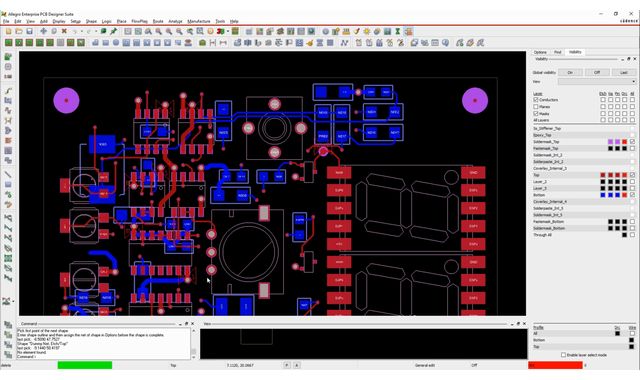

- Allegro PCB Editor, Cadence Allegro PCB DesignTrue DFMテクノロジ, ケイデンス・デザイン・システムズ

米ケイデンス・デザイン・システムズは2017年9月13日、設計作業中にDFM(Design For Manufacture:製造容易性設計)検証をリアルタイムに実行するソリューション「Cadence Allegro PCB DesignTrue DFMテクノロジ」を発表した。

同ソリューションはPCB設計者が製造サインオフを行う前の早期設計段階でデザインルールエラーを発見し、修正することを可能にするもので、Allegro PCB Editorに搭載される。早期にエラーを発見することで設計のやり直しや設計サイクルを削減し、新製品開発や導入プロセスの時間を短縮できる。

バッチモードでDFM検証を行う従来の検証ツールとは異なり、設計作業中にリアルタイムに検証結果をレポートするため、PCB設計者とDFM検証チーム間で設計/検証/修正の繰り返しとなるのを防ぐ。設計者が最終的なDFMサインオフ段階に達するまでには、製造ルールは満たされているため、製造側にスムーズにデータを引渡すことができる。

ケイデンスのAllegro constraint-driven設計フローや電気的、物理的ルール、およびスペーシングルールに用いられているオンライン検証ソリューションと両立が可能で、トレース、ピン、ビアなどの銅箔オブジェクト同士や、ボード外形とのスペーシングを電気的およびネットベースのルールに関係なく、リアルタイムで検証できる。

また製造ルールの設定、適用、再利用を容易に行うことができる。DFMルールの入出力機能を備え、2000以上のチェック項目をサポートする。同じクラスのエラーをまとめて扱うことができる新しいDRCブラウザを採用。制約条件の有効/無効はルールカテゴリー全体、グループ、あるいは個々のルールに対し構成定義できる。ルール適用の対象は、エッチ、非エッチ、及びスタックアップの3モードが用意され、設計者はレイアウト層、ジオメトリ、カットアウトなどを分けてチェックできる。

その他、グラフィックを用いたルール解説やDRCのタイプによる識別機能、DRCエラーのカウントチャート機能も提供。DRCエラーのソート、表示やレビュー、チェックの適応停止や解除も簡単に行うことができる。