- 2020-12-28

- 制御・IT系, 技術ニュース, 海外ニュース

- 2次元材料, Andras Kis, LANES(Laboratory of Nanoscale Electronics and Structures), Nature, スイス連邦工科大学ローザンヌ校(EPFL), 二硫化モリブデン(MoS2), 人工知能(AI), 学術, 機械学習(ML), 次世代回路, 浮遊ゲート電界効果トランジスタ(FGFET)

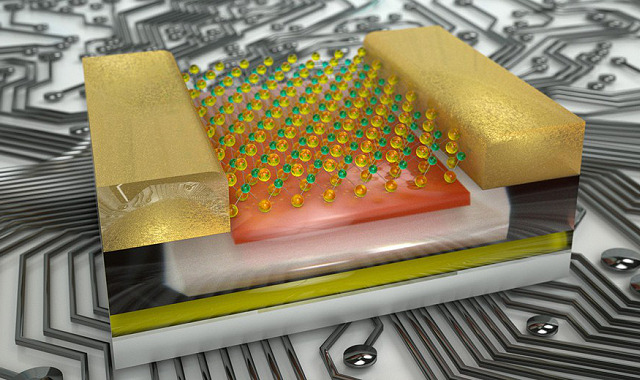

スイス連邦工科大学ローザンヌ校(EPFL)の研究チームは、2次元材料を利用して、ロジックとメモリの2つの機能を単一のアーキテクチャに統合した次世代回路を開発した。小型、高速、高効率のデバイスとして、機械学習(ML)や人工知能(AI)での用途を見込む。研究結果は、2020年11月4日付けで『Nature』に公開されている。

近年、MLを利用したアプリケーションの重要度が増すにつれて、高いエネルギー効率を持つハードウェア開発の需要も増している。従来のノイマン型コンピューターアーキテクチャは、プロセッサとメモリが別々のユニットに分かれている。そのためデータは常に2つのユニット間を行き来する必要があり、時間とエネルギーを浪費することから、次世代型アーキテクチャやそれを構成する材料は重要な研究対象となっている。

新しい半導体材料の一つとして注目されているのが、2次元材料の二硫化モリブデン(MoS2)で、その厚みはわずか3原子分だ。EPFLの研究チームは以前から単層MoS2の特性について研究しており、シリコントランジスタより小型でエネルギー消費が非常に少ないこと、バンドギャップを持たないグラフェンと異なり1.8eVの直接バンドギャップを持ち、トランジスタに適することを報告している。

今回研究チームは、優れた電気特性を持つMoS2を浮遊ゲート電界効果トランジスタ(FGFET)に組み込むことで、論理演算とメモリ機能を統合した1つのアーキテクチャ、いわゆる「ロジックインメモリアーキテクチャ」を構築した。FGFETはカメラなどのフラッシュメモリにも使われ、長時間電荷を保持できるのが特長だ。2次元材料をロジックインメモリに利用するのは初めてだとし、プログラマブルインバーターをはじめ、複数のロジックインメモリを論理ゲートに組み込むことで、より複雑な演算処理ができることを実証している。

「人間の脳の中では、ニューロンが記憶と暗算を同時に実行している。回路に2つの機能を持たせるということは、その働きに似ている」と、研究チーム率いるEPFLのLANES(Laboratory of Nanoscale Electronics and Structures)所長のAndras Kis准教授は語る。

さらに従来のアーキテクチャと比較して「メモリユニットとプロセッサ間のデータ転送に関連するエネルギー損失、計算動作に必要な時間、必要なスペースが削減できる」と、利点を挙げている。2次元材料を使用した回路製造に対する知見も深まり、1回の工程で80個以上のチップを製造可能な工程を開発したとしている。MLやIoT、不揮発性コンピューティング向けに最適な次世代回路の実現が期待される。