- 2021-6-24

- 技術ニュース, 電気・電子系

- 3次元積層半導体, WOWアライアンス, ウエハー, キャパシタ内蔵Siインターポーザ, バンプレスChip-on-Wafer(COW), 東京工業大学, 研究, 電源基板

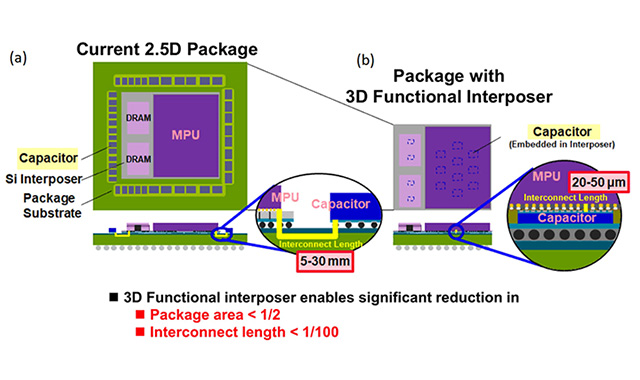

半導体パッケージ構造(左:現状の2.5Dパッケージ、右:開発した電源基板を用いた3Dパッケージ)

東京工業大学は2021年6月22日、WOWアライアンスとの共同研究により、低消費電力/超小型の電源基板「キャパシタ内蔵Siインターポーザ」を開発したと発表した。手法として、バンプを使わないウエハーレベルのパッケージ化プロセスであるバンプレスChip-on-Wafer(COW)を創出したという。

現在、2次元での微細化による半導体デバイスの高性能化に限界が迫っていることから、さらなる高性能化、低消費電力化を目指した3次元積層半導体の開発が進められている。しかし、3次元積層による半導体のパッケージ化では、蓄電装置であるキャパシタと半導体の間の配線が長くなり、伝達スピード低下の一因となる寄生容量も大きくなるという問題があった。

そこで研究では、抵抗率の低い銅配線を用いた伝送路であるCuインターコネクトを採用しながら、Siインターポーザにキャパシタを内蔵できるバンプレスCOWプロセスを開発し、従来に比べ半導体とキャパシタの間の配線長を1/100に短縮することで、超小型で低消費電力な電源基板とすることを目指した。

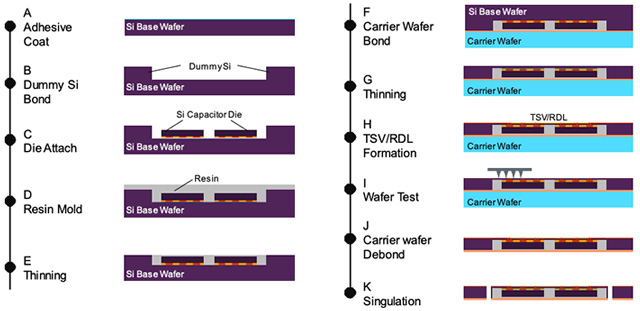

キャパシタをSiインターポーザに内蔵する方法として開発したバンプレスCOWプロセスは、まず接着剤(adhesive)を直径300mmのSiベースウエハーに5μmの厚さで塗布する。その接着剤の上にキャパシタを搭載して接着剤を硬化させ、Siベースウエハーとキャパシタとを接着させる。

次に、エポキシ樹脂(resin)でSiベースウエハー全体を低圧でコンプレッション(モールド)成形し、その樹脂を薄化(thinning)。その後のCOWプロセス中のウエハー反りを最小化するため、ベースウエハーを裏返し、強化材として厚さ300mmのSiキャリアウエハーを薄化した樹脂側に接合する。その上で、ベースウエハーの厚みを775μmから20μmまで薄化し、TSVとRDLを形成することでキャパシタとRDLを接続させる。

研究では、このキャパシタとRDLの接続後にウエハーテストを実施。電源基板の電気特性を評価した。実装する際は、Siキャリアウエハーを除去し、切り離したものを使用する。

バンプレスCOWプロセスフロー

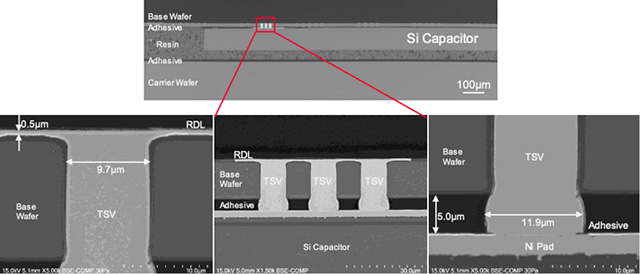

バンプレスCOWプロセスによって作製した電源基板のTSVとキャパシタ端子の接続部の断面を観察した結果、クラックや剥離などの欠陥はなかった。特にTSVとキャパシタ端子の間にも酸化膜残渣などは確認されず、良好な接続が得られたという。

キャパシタを内蔵した電源基板の断面写真

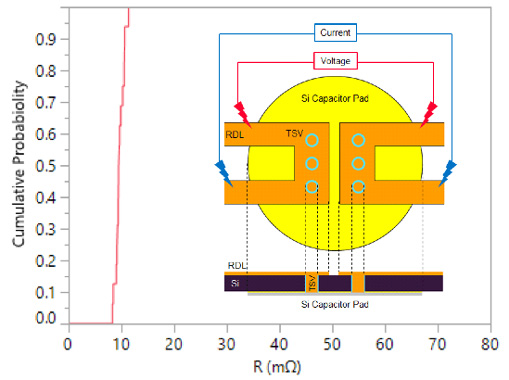

TSVの接続抵抗を電源基板の電気特性として測定した結果では、10mΩで極めて安定しており、Siインターポーザに内蔵されたキャパシタに反りや収縮がほとんど発生していないことが明らかになった。

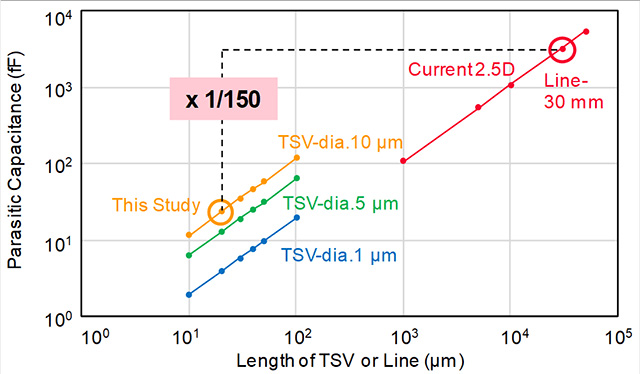

この評価によって得られたTSV接続抵抗を前提に、今回開発した電源基板を使った場合の配線長の短縮による寄生容量の低減効果を計算。その結果、従来に比べ寄生容量が1/150に小さくなるという数値が算出された。

TSVの接続抵抗

配線長の短縮による寄生容量の低減効果

3次元積層半導体のパッケージに、開発した電源基板のキャパシタ内蔵Siインターポーザを用いることで、半導体パッケージの低消費電力化/超小型化に貢献することが期待される。今後は、このキャパシタ内蔵Siインターポーザと3次元積層半導体をバンプレスTSV配線による3次元化技術で直接接続し、半導体パッケージの低消費電力化/超小型化の実証を目指す。