- 2021-7-24

- 制御・IT系, 技術ニュース, 海外ニュース

- AIプロセッサ, ASIC, Google, Google Hardware and Architecture, Google Research, TPU(Tensor Processing Unit), グラフ畳み込みニューラルネットワーク(GCN), コンピューターチップ, デナード則, フロアプランニング, ムーアの法則, 学術, 強化学習問題, 機械学習, 深層強化学習

Googleは、機械学習のひとつ、深層強化学習を利用して、コンピューターチップを短期間で設計する手法を開発した。その手法を使うと、通常数カ月かかる処理を6時間以下に短縮し、性能や消費電力は同等かそれ以上のチップデザインを導き出せる。既に、次世代のAIプロセッサ「TPU(Tensor Processing Unit)」の設計にも利用された。研究結果は、2021年6月9日付けの『Nature』に掲載されている。

ムーアの法則とデナード則の速度が鈍化する一方、人々がコンピューターに求める性能は指数関数的に増加している。コンポーネントや配線など、コンピューターチップの物理的なレイアウトを決める「フロアプランニング」は、チップの性能に関わる重要な作業だ。しかし、過去50年にも及ぶ研究にも関わらず、この工程は自動化できていないため、専門のエンジニアが多くの時間と労力をかけて製造可能なレイアウトを作成している。

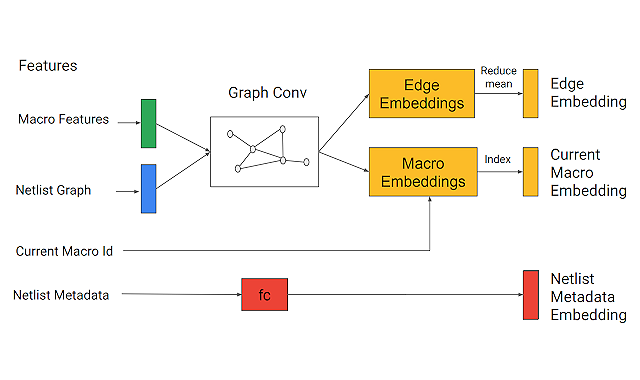

今回、Google ResearchとGoogle Hardware and Architectureのチームは、フロアプランニングを「強化学習問題」として提示し、グラフ畳み込みニューラルネットワーク(GCN)を構築。1万個のラベル付き配置パターンを使ってGCNを訓練し、最適なチップ配置を割り出した。これは、AIがフロアプランニングという名のボードゲームをしているようなもので、具体的にはチップのコンポーネントが駒、基板がゲーム盤で、制約条件を満たしつつ消費電力などを最小化するようにチップを動かしている。

最新のアクセラレータに対するフロアプランニングを人間とAIで比較すると、人の手では許容可能なフロアプランを作成するのに数カ月かかったのに対し、AIは6時間以内に完了しただけでなく、消費電力、性能、チップ面積などあらゆる指標で、人の手による設計解と同等もしくは上回っていた。

さらに、このAIは過去の経験から学び、時とともに改善していくことができる。特に、チップブロックの訓練数が増えるにつれて、見たことのないチップブロックに遭遇した場合でも、より良い配置を即座に生成できるようになった。このようにAIを活用すれば、世代が変わるごとに費やしていた何千時間もの労力が節約できる可能性がある。

今回はTPUの最適化を提示したが、ASICなど他のチップにも応用できるという。AI自身がチップ設計サイクルを短縮できるようになれば、AI設計の強力なハードウェアがAIの発展を促進するというように、AIとハードウェアの間に共生関係を構築できるだろうと、研究チームは考えている。