- 2023-4-27

- 制御・IT系, 技術ニュース

- AIアクセラレーター, CMOS, EMP, NNアクセラレータ, PIM型, PIM型NNアクセラレータ, PIM型マクロ, ULVR-SRAM, ニューラルネットワークアクセラレータ, プロセッシング・イン・メモリ, マクロ, モバイルエッジデバイス, 東京工業大学, 東京工業大学科学技術創成研究院, 研究

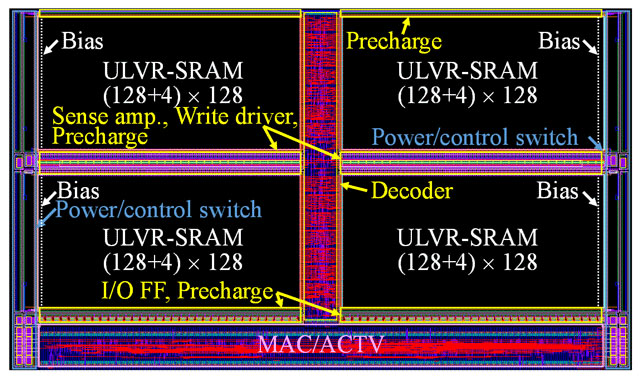

東京工業大学は2023年4月26日、同大学科学技術創成研究院の研究グループが、エネルギー最小点(EMP)動作で動作時電力を99%削減し、また、パワーゲーティング(PG)によって重みデータを失うことなく待機時電力を84%削減できるプロセッシング・イン・メモリ(PIM)型のニューラルネットワーク(NN)アクセラレータのマクロを開発したと発表した。CMOSのみで同技術が構成できる。

将来のスマート社会では、AI技術をスマートフォンなどのスマートモバイルエッジ階層のコンピューティングシステムに導入することが期待されており、動作時電力、待機時電力が低く、エネルギー効率の高いNNアクセラレータが要求されている。

様々な構成方法があるNNアクセラレータだが、processing-in-memory(PIM)型のハードウェアがNNアクセラレータの高性能化に有効であり、特にSRAMを用いたPIM型NNアクセラレータは、現状のCMOS技術で実装できるため、応用上重要である。

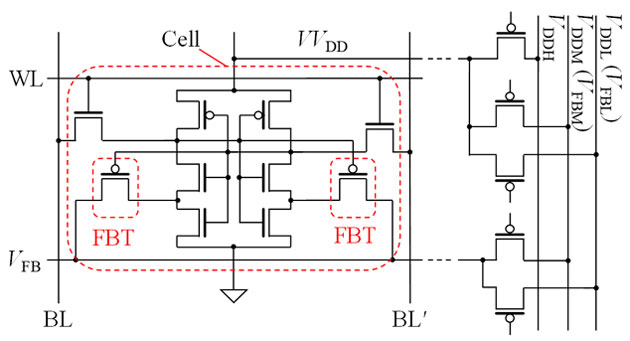

研究グループは最近、通常電圧下(VDD)では従来のSRAMと同様の高性能SRAM動作をし、0.2V程度の超低電圧(VUL)でもデータを失うことなく保持できる超低電圧リテンションSRAM(ULVR-SRAM)セルを提案した。

提案したULVR-SRAMセルの回路構成

ULVR-SRAMは、SRAMであっても大幅に待機時電力を削減でき、EMP動作にも対応する可能性がある。ULVR-SRAMをPIMのSRAM部に用いることで、PGとEMP動作ができるNNアクセラレータを実現できると考えられ、これまでのSRAM技術では到達できない高いエネルギー効率を実現できる可能性がある。

研究では、EMPで動作し、PGが可能なULVR-SRAM技術を新たに開発。これを用いたPIM型NNアクセラレータのマクロ技術を開発した。開発したULVR-SRAMは、通常電圧VDD(=1.2V)での高性能SRAM動作、EMPとなる電圧VEMP(=0.4V)を用いた最大エネルギー効率SRAM動作、超低電圧VUL(=0.2V)を用いたデータ保持(ULVR)による実質的なPGの3モード動作を実現できる。

研究でははじめに、この3モード動作ができるULVR-SRAMセルの設計技術を開発。設計指標には、各動作モードでのノイズマージンと、ULVRモードでのリーク電流を用いている。PIM型NNアクセラレータ・マクロの設計には、最適設計されたULVR-SRAMセルを用いた。今回、NNのアーキテクチャには、2値化ニューラルネットワーク(BNN)を用いている。

開発したBNAマクロのPG性能について調べ、待機電力削減効果を評価したところ、PGによって、待機時電力を84%削減(クロックゲーティング時のスタンバイ状態からの比較)できた。これは従来の6TセルのSRAMを用いた場合の待機時電力と比べ、94%の削減率となる。

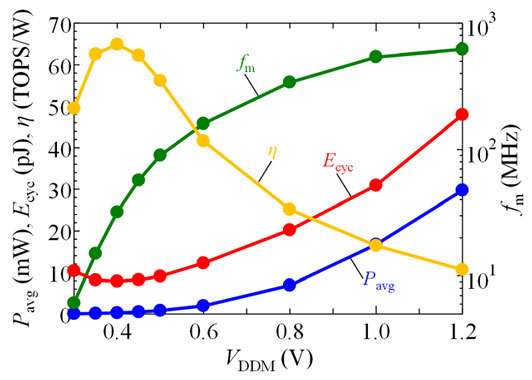

推論動作時の性能評価では、電源電圧(VDDM)の減少とともに平均動作時電力(Pavg)と動作周波数(fm)は減少し、0.4Vで消費エネルギー(Ecyc)が最小となる。VEMPの動作点では通常電圧動作(1.2V)と比べ動作周波数fmは10分の1となるが、大幅に動作時電力が削減されて100分の1になる(99%減)。また、BNAにおける推論のエネルギー効率ηは、VEMPである0.4Vで最大となり、65 TOPS/Wと極めて高い値を実現できる。

消費エネルギーEcyc、平均動作時電力Pavg、動作周波数fm、エネルギー効率ηの電源電圧VDDM依存性

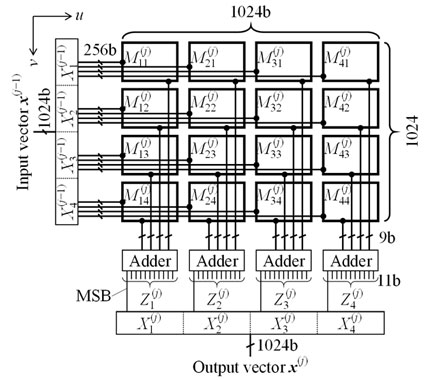

複数のBNAマクロを用いることで、任意のサイズ、形状のネットワークを構成できる。BNAマクロを用いた1024ノードの全結合層の構成例では、Muv(j)が1つのBNAマクロを表し、この場合は16個のマクロと追加の加算器で容易に全結合層を構成できる。

開発したBNAマクロを用いた全結合層の構成例

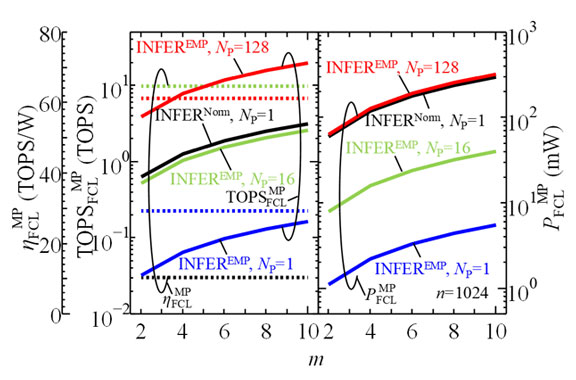

このマクロを用いてMAC演算の適切な並列化を行いEMP動作させることで、通常電圧動作時や従来技術に比べて、演算能力が同じであれば、10分の1程度の消費電力で済み、また、消費電力が同じであれば、10倍程度の演算能力を実現できる。全結合層を用いたベンチマークから、このEMPによる推論では、65TOPS/Wもの高いエネルギー効率を示している。

メモリー部にULVR-SRAMを用いたPIM型NNアクセラレータは、待機時電力の削減効果を大きくとれ、また、エネルギー効率に優れ、消費電力の削減、演算能力の高性能化を実現できる。

全結合層の平均動作時電力PFCLMP、演算能力TOPSFCLMP、エネルギー効率ηFCLSup>MP

AI技術をモバイルエッジ階層で実現できれば、クラウドを介した通信のレイテンシの問題を解消することができ、また、クラウドとの非接続状態でも使用できる。開発した技術は、新しいSRAM技術(ULVR-SRAM)を用いて構成したPIM型NNアクセラレータのマクロ技術で、将来のスマート社会で重要/必要となってくるモバイルエッジデバイスへ搭載できる低消費電力/高性能AIアクセラレータ技術となる。

今後は、開発したマクロ技術をたたみ込み層などにも応用していく。また、ユーザーフレンドリなマクロベースの設計技術の確立を目指す。

関連情報

エネルギー最小点で動作するAI半導体(ニューラルネットワーク・アクセラレータ)技術の開発に成功 モバイルエッジ高性能AI技術 | 東工大ニュース | 東京工業大学