- 2020-1-8

- 制御・IT系, 技術ニュース, 海外ニュース

- Nature Electronics, インテル, ゴードンムーア, シリコンチップ, タッチパッド, ディスプレイ, トランジスタ, プロセッサ, ミシガン大学, ムーアの法則, 学術, 酸化亜鉛スズ(ZTO:Zinc-Tin-Oxide), 集積回路

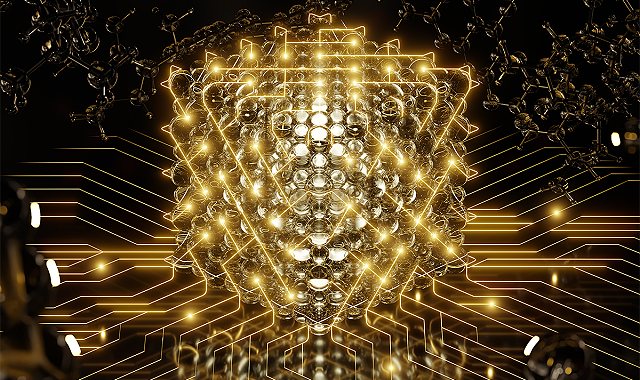

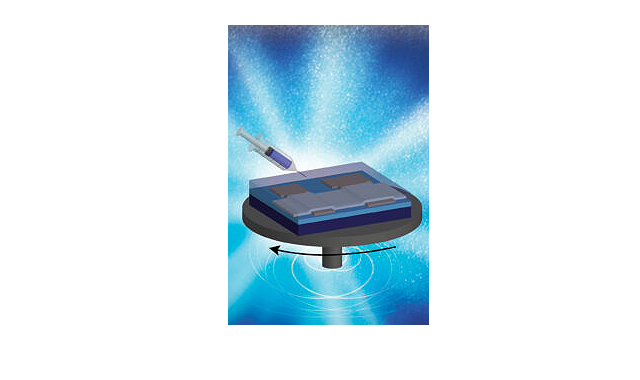

Image credit: Youngbae Son and Rose Anderson, Peterson Lab

ミシガン大学は、集積回路上にトランジスタの第2層を積層することで、低電圧で作動するプロセッサと高電圧ユーザーインターフェースの間の、高電圧と低電圧の信号変換用チップを不要にする設計手法を提案した。研究成果は2019年11月18日、『Nature Electronics』誌に掲載された。

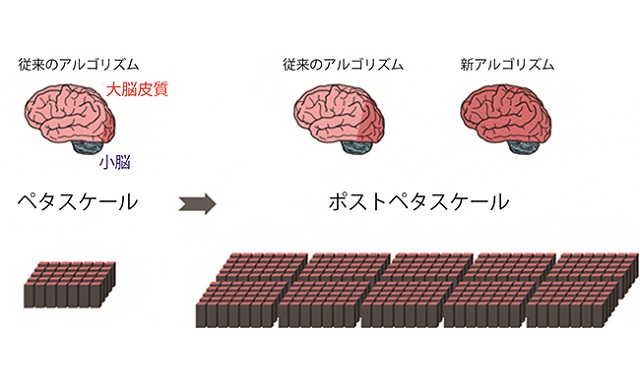

インテルの創業者ゴードン・ムーア氏が提唱した、半導体の集積率はおよそ2年で2倍になるというムーアの法則が知られている。近年トランジスタの微細化が進み、電力効率が高まるにつれて、その作動電圧も低下した。一方で、こうした最先端のチップは、タッチパッドやディスプレイといった高電圧のユーザーインターフェース部品と直接的な互換性がなく、追加のチップによって信号を変換するか、より高い電圧で作動する低集積度のプロセッサを使用せざるを得ないといったトレードオフが課題となっている。

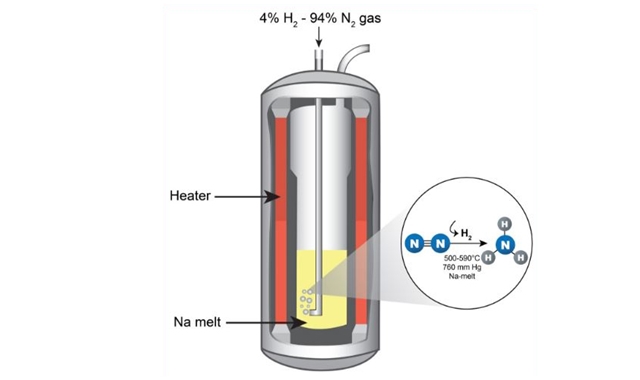

これを解決するため、今回研究グループは、微細なシリコンチップの上に、より高い電圧で差動するトランジスタの第2層を直接積層する設計手法を提案している。この第2層に外部とインターフェースするための高い電圧を処理させることで、現在のトレードオフを乗り越えるというものだ。

具体的には、シリコンチップの上に、アモルファス金属酸化物を積層した。まずシリコンチップを傷つけないよう、チップを亜鉛とスズを含む溶液で覆い、回転させて均一にコーティングした。その後、チップを短時間加熱して乾燥させるというプロセスを繰り返し、厚さ約75ナノメートル、人間の髪の毛の約1000分の1の厚さの酸化亜鉛スズ(ZTO:Zinc-Tin-Oxide)トランジスタの層を形成した。ここに、垂直薄膜ダイオードとショットキーゲートトランジスタの回路要素を構成することで、インバータとして機能させ、低電圧のシリコンチップと高電圧をインターフェースする仕組みだ。ダイオードは、ワイヤレス信号をシリコントランジスタ用のDC電力に変換するために使用している。

研究チームは、ベースとなったシリコンチップが正常に機能していることを確認したうえで、今回の実証は、ムーアの法則を超えるシリコン集積回路への道を開くものだと、説明している。

関連リンク

Beyond Moore’s Law: Taking transistor arrays into the third dimension