- 2016-7-28

- ニュース, 製品ニュース, 電気・電子系

- 3次元フラッシュメモリ, BiCS FLASH, 東芝

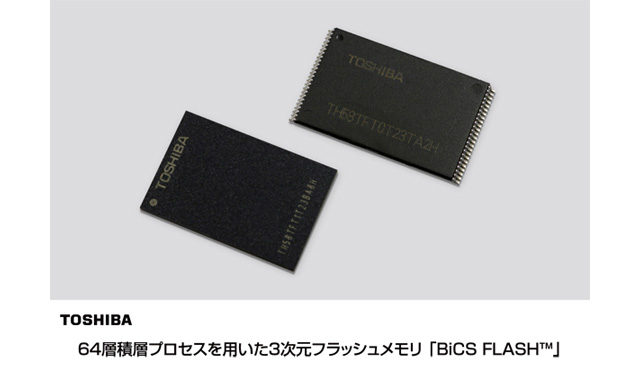

東芝は2016年7月27日、3次元フラッシュメモリ「BiCS FLASH」の64層積層プロセスを開発し、サンプル出荷を順次開始すると発表した。

BiCS FLASHは、従来のシリコン平面上にフラッシュメモリ素子を並べたNAND構造ではなく、シリコン平面から垂直方向に素子を積み上げ、素子密度を向上させた3次元構造のNAND(3D NAND)型フラッシュメモリだ。

同社では、2007年に3次元積層構造を用いたフラッシュメモリを公表して以降、メモリの大容量化、小型化などを目指してフラッシュメモリの3次元積層構造化を進めている。

同製品は、回路技術やプロセスを最適化することでチップサイズを小型化し、これまでの48層積層プロセスを用いたBiCS FLASHと比べ単位面積あたりのメモリ容量をさらに約1.4倍に大容量化。また、チップサイズの小型化により1枚のシリコンウェハーから生産されるメモリ容量を増やし、ビットあたりのコストを削減している。

今回の製品は、256ギガビット(32ギガバイト)の3ビット/セル(TLC)で、2017年前半の量産開始を予定している。データセンター向けエンタープライズSSDやPC向けSSD、スマートフォン、タブレット、メモリカードなどを中心にニーズに合わせて展開していくという。製造は2016年7月に竣工した、同社四日市工場の新・第2製造棟で行われる予定だ。

さらに今後、64層積層プロセスを用いた512ギガビット(64ギガバイト)のBiCS FLASHの製品化も計画しているという。