- 2024-2-20

- ニュース, 技術ニュース, 電気・電子系

- 2次元フェーズドアレイ, 300GHz帯, 6G, CMOS, ISSCC 2024, NTT, フェーズドアレイ送信機, 東京工業大学, 研究

東京工業大学は2024年2月19日、NTTと共同で、CMOS集積回路による300GHz帯フェーズドアレイ送信機を開発したと発表した。

300GHz帯は利用できる周波数帯域が多く残されており、同帯域における100Gbps以上の超高速6G無線通信サービスの実用化が期待されている。そのような高い周波数では、空間伝搬損失を補うことができるレベルの高い送信電力を持つ送信機を実現する必要がある。

それを実現するために、複数のアンテナ出力を合成/制御することでアンテナ利得を高めてビームステアリングができる、2次元フェーズドアレイ技術の研究が進められてきた。しかし、フェーズドアレイは多くの送信回路を使用するために必要な出力電力も大きくなる。シリコンCMOSプロセスは安価で量産性や集積化に優れるが、トランジスタの動作周波数が制限されるため、同周波数帯での高性能な電力増幅器の実現が難しかった。

また、CMOS集積回路では十分な出力電力が得られず、チップ面積も大きくなることから、実用には十分ではなかった。

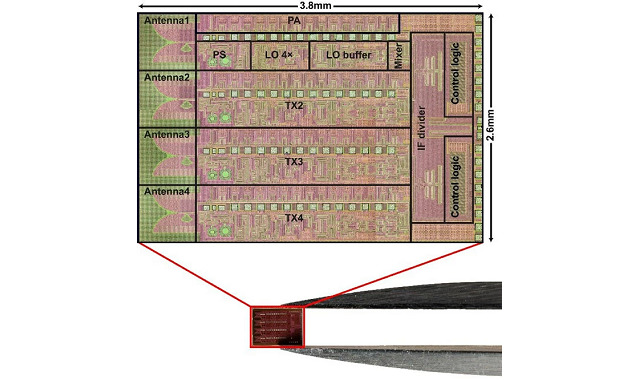

今回開発した300GHz帯フェーズドアレイ送信機は、65nmシリコンCMOSプロセスを用いて設計。CMOSにおいても300GHz帯で動作するよう、トランジスタのレイアウトを新たに最適化した。これにより250~300GHz帯での利得が従来から大幅に向上し、300GHz帯での電力増幅器の設計が可能になった。

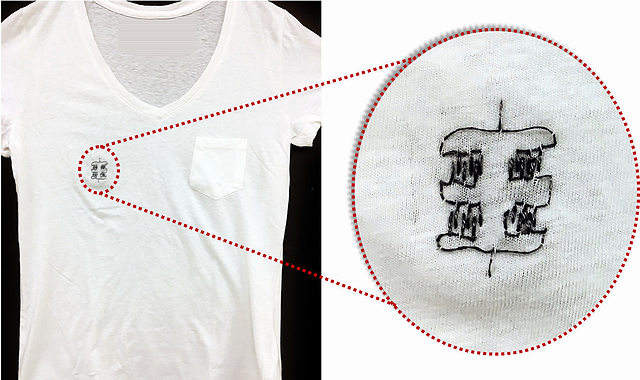

さらに、サブハーモニックミキサ、移相器、4逓倍器付きのLO回路の構成を工夫することで、従来の5分の1の面積に小型化。4系統の送信回路を3.8×2.6mmの1チップに集積した。

実際に65nmシリコンCMOSプロセスを用いて、300GHz帯送信機ICチップを作製。4系統の送信回路を持つCMOS ICチップをプリント基板上に4つ並べて実装して16アレイのフェーズドアレイ送信機を構成した。さらに、この基板を4枚重ねて張り合わせることで、16×4の2次元フェーズトアレイ送信機を実現した

作製した送信機の1系統の送信回路の送信レートを測定したところ、16QAM変調時に108Gbps、32QAM変調時に95Gbpsとなり、100Gbpsを超える送信レートであることが確認できた。

今回の安価で量産性に優れたCMOSプロセスでの300GHz帯の送信機の実現は、同周波数帯での6G高速無線通信の実現に貢献することが期待できるという。同大学では今後、さらに多くの送信回路を集積したフェーズドアレイ送信機の開発を目指す。

なお、本研究成果は、同年2月18日〜22日までアメリカ・サンフランシスコで開催される「ISSCC 2024(国際固体素子回路会議)」で発表される。

関連情報

オールCMOSの300 GHz帯フェーズドアレイ送信機を開発 100 Gbps超のデータ速度を達成、6G無線機の実現へ大きく前進 | 東工大ニュース | 東京工業大学