全結合型アニーリングプロセッサーLSI「STATICA」

東京工業大学は2020年2月18日、科学技術創成研究院の本村真人教授らと北海道大学、日立北大ラボ、東京大学が共同で、組合せ最適化問題を高速に解く新しいアニーリング処理方式「ストカスティック・セルラー・オートマタ(SCA)」と、それを用いた全結合型アニーリングプロセッサーLSI「STATICA」を開発したと発表した。STATICAは、既存の手法に比べ、アニーリング処理の性能を少なくとも数倍、エネルギー効率を2桁以上向上させることができる。

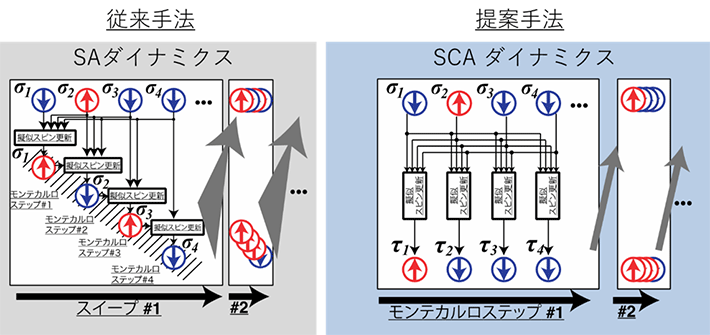

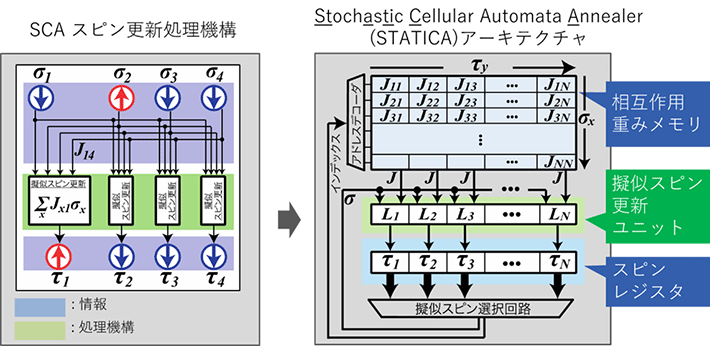

SCAは、全疑似スピンの値を並列に更新可能である点を特徴とする。従来のアニーリングマシンは、基本的に「シミュレーテッド・アニーリング(SA)」もしくはそれに類似する計算方法をベースにしているが、SAではある疑似スピンの値が変化すると、これとつながる全ての疑似スピンへの影響を改めて計算する必要がある。このため、疑似スピンの値の更新は逐次的なものになっていた。

SAとSCAの比較

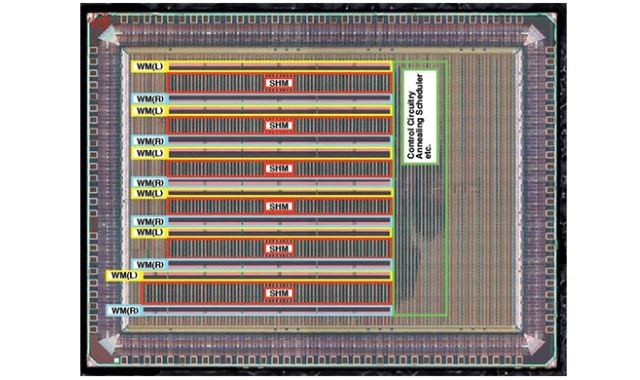

SCAにおいては、更新したい疑似スピンにかかる相互作用係数を読み出し、現在の疑似スピンの値と演算することで並列な疑似スピン更新が行われる。研究チームは、相互作用係数をメモリに書き込み、そのメモリから並列に相互作用係数を読み出し、メモリに付随したロジック回路で並列演算することで効率よくSCAの計算を行えることを発見し、このロジックのアーキテクチャをSTATICAと名付けた。

STATICAアーキテクチャ

研究チームはこのアーキテクチャに基づき、TSMCの65nmプロセスを用いて全結合型アニーリングプロセッサーLSIであるSTATICAを試作した。3×4mmサイズで512疑似スピンからなるイジングモデルのアニーリング処理を並列に実行できるもので、消費電力は600mW程度となっている。

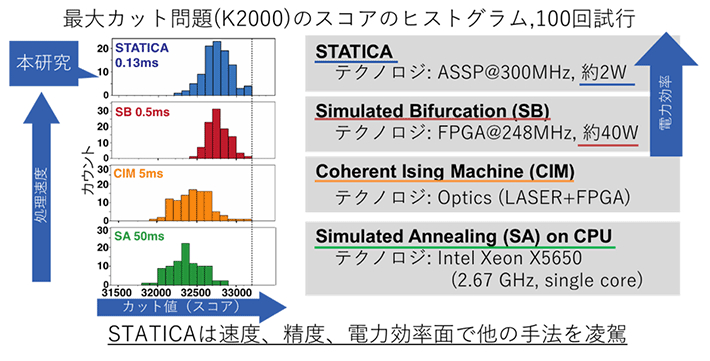

最近、全並列型アニーリングマシンが注目されるようになり、いくつかのマシンが提案されている。そのような既存技術と比べ、STATICAはアニーリング速度/消費電力/答えの精度のいずれにおいても、高い指標を達成することができる。

STATICAと既存の全並列型アニーリングマシンの比較

研究チームは今後、STATICAのキャパシティ強化を進めるとともに、ディープラーニングや機械学習などを含む情報処理システムへの統合に取り組み、早期の実用化を目指す。