- 2024-2-22

- 制御・IT系, 製品ニュース

- 22nmロジック混載MRAMプロセス, ISSCC 2024, MRAM, MRAMメモリセルアレイ, OTP, STT-MRAM, カスコード接続, スピン注入磁化反転型磁気抵抗メモリ, マイコン, マイコンテストチップ, リードウィンドウ, ルネサス, ルネサス エレクトロニクス, 高速書き換え技術, 高速読み出し技術

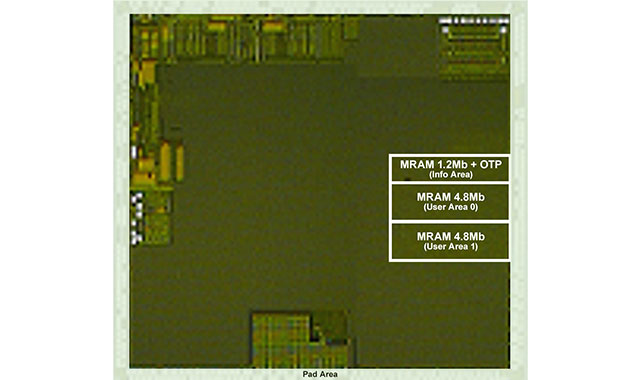

ルネサス エレクトロニクスは2024年2月21日、スピン注入磁化反転型磁気抵抗メモリ(STT-MRAM、以下MRAM)の読み出しと書き換え動作を高速化する技術を発表した。22nmロジック混載MRAMプロセスで、10.8MbitのMRAMメモリセルアレイ搭載のマイコンテストチップを試作し、ランダムアクセス周波数200MHz超と、書き換えスループット10.4MB/sを達成している。

MRAMは、従来のマイコンに搭載されているフラッシュメモリに比べ、読み出しマージンが小さく、読み出し速度の高速化に課題があった。一方、書き換え動作は、消去動作が不要でフラッシュメモリに比べ高速だが、通常使用時だけではなく、テスト工程でのテストパターンやセットメーカーでのコードの書き込み時間の短縮によるコスト低減が求められている。

今回、MRAMの高速読み出し、高速書き換えのための回路技術を開発し、これらの課題に対応。世界最速となるランダムリードアクセス時間4.2nsを達成し、MRAMの出力データを受けるインタフェース回路のセットアップ時間を考慮しても、200MHzを超える周波数でのランダムリード動作を実現した。

一般にMRAMの読み出しは、メモリセル電流と参照電流を差動増幅回路(センスアンプ)で比較して、その大小関係を判定し、読み出しするが、フラッシュメモリに対して”0”状態と”1”状態のメモリセル電流の差(リードウィンドウ)が小さいため、高速リードのためには、参照電流をリードウィンドウの真ん中に正確に合わせ込む必要がある。

開発では構成を、テスト工程でチップごとに実際のメモリセルの電流分布を見て、ウィンドウの中心が参照電流と一致するように調整する機構と、センスアンプのオフセットを低減する機構とし、読み出しはこれらを調整して高速化した。

また、従来構成では読み出し動作に時間がかかる要因となっていた、リード動作時にビット線の電圧を抑制する回路部分をカスコード接続構成とし、この部分の寄生容量を低減して、高速化している。

書き換え動作は、2021年12月に発表した「混載メモリ用STT-MRAMの高速書き換え技術」で高速化していたが、今回、テスト工程やセットメーカーでの書き込み時には電源環境が安定し、外部電圧の下限電圧を高くできることに着目して、第一段階で全ビットに印加する外部電圧からの降圧電圧を高く設定。書き込みスループットを1.8倍高速化している。

10.8MbitのMRAMメモリセルアレイを搭載したマイコンテストチップは、これらの新技術の組み合わせで試作。評価の結果、最大接合温度125℃で、200MHz超のランダムアクセス読み出し周波数と、書き換えスループット10.4MB/sを達成した。

開発したテストチップには、一度書き込むと改ざんできない0.3MbitのOTPを、MRAMのメモリセルの絶縁破壊を用いて搭載している。通常、OTPの書き込みには、MRAM書き込みよりも高電圧の印加が必要となる。特にフィールドでの書き込みの難易度が高くなるが、メモリセルアレイ内の寄生抵抗を抑えるように工夫し、フィールドでの書き込みにも対応している。

今回開発した技術を適用することで、MRAMのメモリアクセスのスピードは200MHzを超えるレベルまで改善され、MRAMを搭載するマイコンを高性能化できる。さらに書き換え時間の高速化で、エンドポイント機器でのコード書き換えの効率化に貢献する。

なお、本研究成果は、同年2月18日〜22日までアメリカ・サンフランシスコで開催されている「ISSCC 2024(国際固体素子回路会議)」で発表された。

関連情報

高性能マイコン向けに、200MHz超の高速ランダムアクセス読み出し、10.4MB/sの高速書き換えを実現したロジック混載MRAMマクロを開発 | Renesas