- 2025-3-18

- ニュース, 半導体, 技術ニュース, 電気・電子系

- 3端子パッケージ, NEDO, ゲート駆動ICチップ, スイッチング損失, パワー半導体, 新エネルギー・産業技術総合開発機構, 東京大学, 研究

新エネルギー・産業技術総合開発機構(NEDO)は2025年3月17日、同機構が実施する事業において、東京大学を中心とする研究グループが、パワー半導体のスイッチング損失を自動低減する技術を3端子パッケージのパワー半導体にも適用することに成功したと発表した。

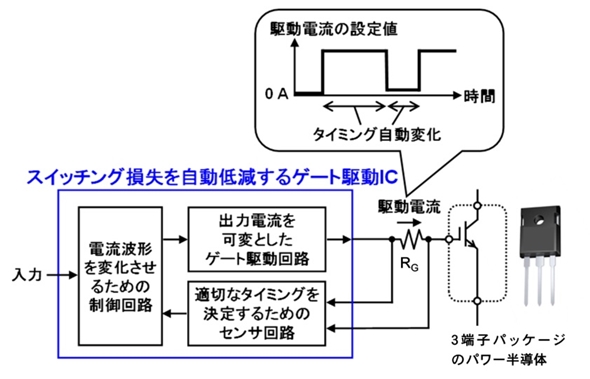

同研究グループは2023年に4端子パッケージのパワー半導体のスイッチング損失を自動低減する「ゲート駆動ICチップ」を開発した。しかし4端子パッケージのパワー半導体の品種数は全体の2割程度あったため、その適用範囲が限られていることが課題だった。

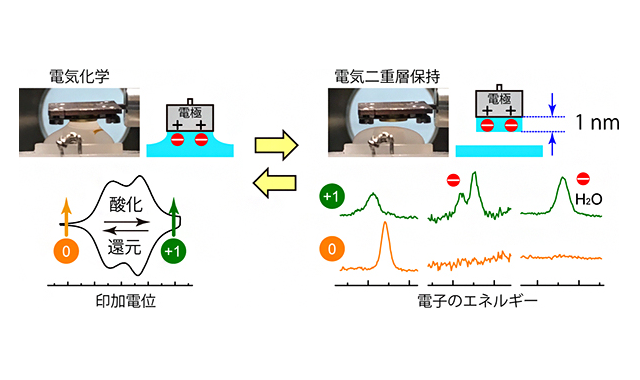

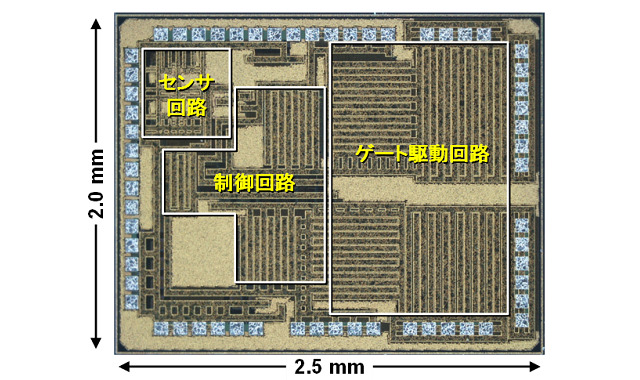

今回同ゲート駆動ICチップのセンサー回路を改良し、パワー半導体の駆動電流をセンシングする方法を採用することで、3端子パッケージのパワー半導体にも適用可能にした。開発したゲート駆動ICチップによる3端子パッケージパワー半導体のスイッチング損失の低減効果を確かめるため、さまざまな条件で検証を実施した結果、16~30%の範囲で低減することが実証された。

今回の改良により、ゲート駆動ICチップが適用可能なパワー半導体の品種が約5倍に拡大する。また、同技術はシリコンだけではなく、炭化ケイ素などのパワー半導体にも適用可能だ。

開発したスイッチング損失を自動低減するゲート駆動ICチップ

今後、NEDOと同研究グループは、さらにスイッチング損失を低減できる自動最適化手法やセンシング誤差を改善したセンサー回路の開発などを進める。

関連情報

パワー半導体のスイッチング損失を自動低減するゲート駆動ICチップの適用範囲を約5倍に拡大します | ニュース | NEDO