京都大学は2020年8月24日、東京工業大学と共同で、SiCパワー半導体を高品質化する独自のSiCの酸化膜形成方法を開発したと発表した。

現在多くの半導体パワーデバイスにはシリコン(Si)が使用されているが、電気のエネルギー変換(電力効率)の観点からは、Siによるデバイス性能は理論上限界に達しつつある。今後大幅な電力効率の向上を実現させるためにはSiに替わる新しい半導体材料が必要になる。その材料として期待されているのがSiC(シリコンカーバイド、炭化ケイ素)だ。

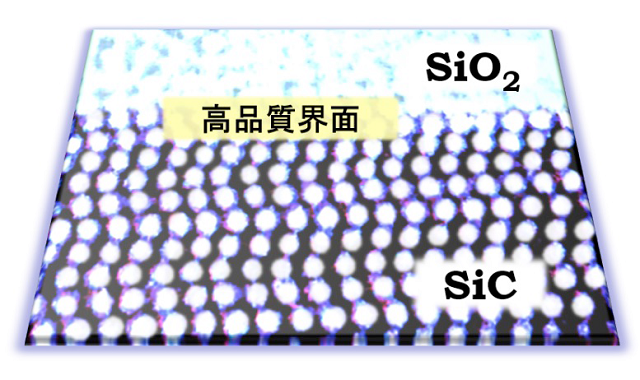

SiCは絶縁破壊や熱に対する耐性が非常に優れ、高耐圧、低損失のパワーデバイス用材料として全世界で研究開発が進められている。近年、エアコンや産業用モーター、電車や電気自動車などにSiCパワー半導体が搭載され、省エネルギー効果が実証されている。しかし、SiCトランジスタの重要な部分である酸化膜とSiCの境界部分(界面)に多くの欠陥が存在することが、SiCトランジスタの特性や信頼性を制限しており、本来のSiCトランジスタの性能を発揮できない状態が続いていた。

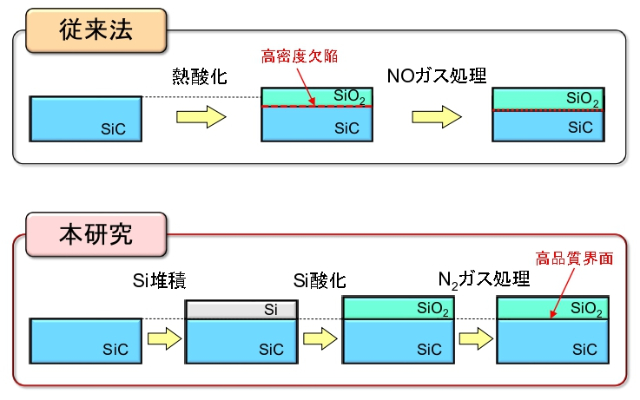

従来、Siと同様の製法で、SiCに熱を加えて酸化してSiO2膜を形成することでSiCトランジスタを作製してきた。今回この方法では界面に炭素原子に起因する欠陥が高密度に形成されることを第一原理計算により突き止めた。そして上記に替わる独自の酸化膜形成方法を開発した。

まず、清掃なSiC表面にSiを堆積して低温で酸化することでSi薄膜をSiO2膜に変換。この方法によって高品質のSiO2膜を形成した。Siの酸化開始温度はSiCのそれより低温のため、SiCを酸化させずにSi薄膜をSiO2に変換できる。

さらに従来の一酸化窒素(NO)による界面への窒素原子導入を、高温の窒素(N2)ガス雰囲気による熱処理に変えることで、従来発生していた窒素原子導入によるSiCの酸化および欠陥発生を抑制することに成功した。

SiO2/SiC構造を形成する方法の模式図(上:従来法、下:本研究で提案する手法)

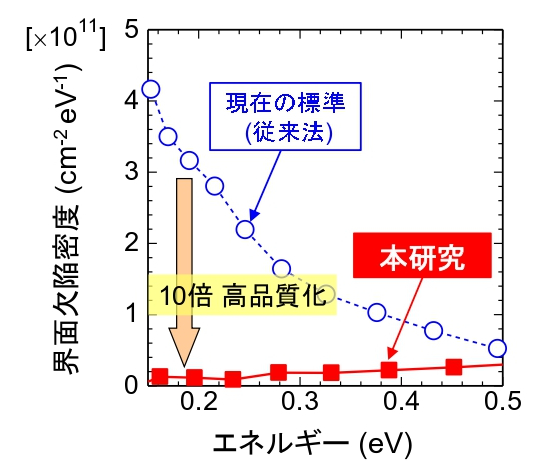

今回の方法で作製したSiO2/SiC界面の欠陥は、従来の世界標準と比較して10倍の高性能化(欠陥量1/10)を実現していることを実験により確認した。具体的には、従来法では1.3×1011cm-2存在した欠陥密度を、独自の方法により1.2×1010cm-2にまで低減することに成功した。

SiO2/SiC界面欠陥の低減を示す実験データ

今回の研究成果により、SiCパワー半導体の実用化を加速させることが期待されるという。またSiCトランジスタに適用することで、大幅な性能向上、チップ面積縮小による低コスト化、さらに信頼性向上ができるという。