- 2022-2-28

- 技術ニュース, 機械系, 海外ニュース

- Gordon Moore, ICチップ, Intel 4004, Intel 4040, Sam Zeloof, Z1, Z2, しきい値, アルミニウムゲート, インテル, カーネギーメロン大学, トランジスター, ビジコン, ポリシリコンゲートプロセス, ムーアの法則

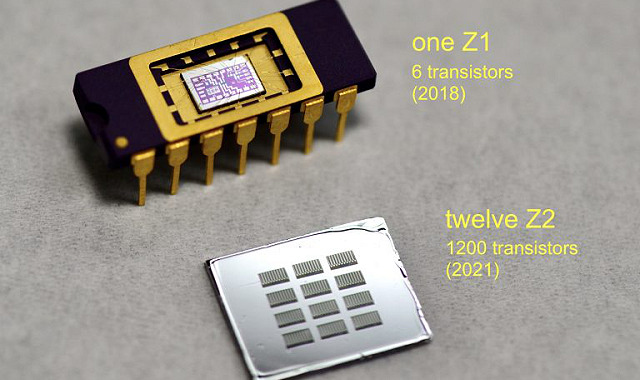

米カーネギーメロン大学の学部生であるSam Zeloof氏は、トランジスター1200個を集積したICチップ「Z2」を自宅ガレージで製造した。同氏は、まだ高校生だった2018年に最初の自作ICチップ「Z1」を製造したが、Z1のトランジスター数は6個だった。

同氏によるICチップ集積密度の向上ペースは、「ムーアの法則」のペースをはるかに上回っている。ムーアの法則とは、米インテル共同創業者の1人であるGordon Moore氏が1965年と1975年に発表した見解をベースにして、研究開発期間と半導体製品の集積密度との関係を物理法則のように定式化したもので、半導体回路の集積密度は1年半~2年で2倍になるとされている。

インテルが日本のビジコンと共同開発した世界初のマイクロプロセッサー「Intel 4004」のトランジスター数は2300個で、その次世代プロセッサー「Intel 4040」のトランジスター数は3000個だったが、Zeloof氏が自作したZ1とZ2のトランジスター数は6個から1200個と実に200倍も増加している。

Z2はゲート長10μmのポリシリコンゲートプロセスにトランジスターを100個搭載しており、10×10のシンプルな配置だ。Z1ではアルミニウムゲートを採用していたためしきい値が10V超と高かったが、ポリシリコンゲートプロセスに変更したことでしきい値は下がり、2.5Vと3.3Vのロジックレベルで駆動するという。

同氏はZ1とZ2を製造したことで、「これぐらい低いトランジスター集積密度でも、もっと面白い回路を作れることは間違いない。プロセスの微調整は必要だが、高品質のトランジスターを安定して作れるようになったので、より複雑なデジタル回路やアナログ回路を設計できるはずだ」と自身のブログで述べている。