- 2024-1-15

- 制御・IT系, 技術ニュース

- CoFeB/MgO, STT-MRAM, スピントロニクス, スピン移行トルク磁気抵抗メモリ, 形状異方性, 微細化技術, 東北大学, 極微細世代半導体集積回路, 界面異方性, 研究, 磁気トンネル接合(MTJ)素子

東北大学は2024年1月11日、半導体の省エネ化につながると期待されているスピン移行トルク磁気抵抗メモリ(STT-MRAM)をナノメートル(10億分の1m)サイズにまで微細化する技術を確立したと発表した。このSTT-MRAMは、大手半導体デバイスメーカーの既存設備でも製造が可能で、活用が期待される。研究成果は2024年1月4日、論文誌npj Spintronicsに掲載された。

電源を切っても情報が保持される不揮発性メモリは、半導体の大幅な省エネ化をもたらすと期待されており、人工知能(AI)や、モノのインターネット(IoT)、車載機器まで幅広いアプリケーションでの利用に向けた研究開発が進められている。特にスピントロニクス技術を利用したSTT-MRAMは、大手半導体デバイスメーカーから10ナノメートル台の大きさの車載向け半導体への導入が発表されるなど注目を集めている。

微細化が進む半導体回路で幅広いアプリケーションに対応するためには、STT-MRAMの記憶素子である磁気トンネル接合(MTJ)素子そのものの微細化とともに、アプリケーションごとに異なる高速性や高温でのデータ保持特性、高速でのデータ書き込みといった要求性能を満たしていく必要がある。

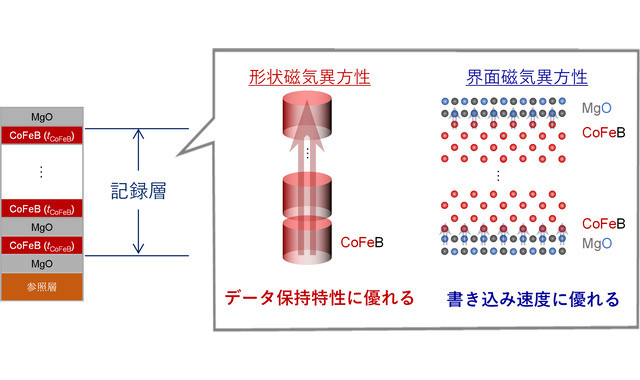

今回、研究グループは、CoFeB/MgOからなる積層磁性層構造のCoFeB層の膜厚と、MgO挿入層の数(積層回数)を変化させることで、界面異方性と形状異方性を独立に制御する方法を考案した。CoFeB層膜厚を直径に対して厚くし、形状磁気異方性が支配的に作用するように設計された構造は、高温でのデータ保持特性に優れている。一方、CoFeB層を薄くしつつ積層回数を増やし、界面磁気異方性が支配的に作用するように設計された構造は高速書き込み性に優れている。

実際に形状磁気異方性が支配的な構造で、直径7.6ナノメートルの素子を作製したところ、150℃で十分に高いデータ保持特性を確認した。一方、界面磁気異方性が支配的な構造で、直径4.5ナノメートルの素子を作製したところ、比較的高いデータ保持特性を示しながら、1ボルト以下、10ナノ秒の電圧パルスでデータを書き換えられることを確認した。

研究グループは今回の成果について「今後STT-MRAMを幅広いアプリケーションに展開するための基盤的理解が構築された」としている。開発した積層磁性層構造は、現在STT-MRAMの材料として主流のCoFeB/MgOが使われており、大手半導体デバイスメーカーの既存設備でも製造できる。このため、将来の極微細世代半導体集積回路に向けたSTT-MRAM開発が加速すると期待される。

関連情報

省エネ半導体の切り札STT-MRAMの極限微細化技… | プレスリリース・研究成果 | 東北大学 -TOHOKU UNIVERSITY-