- 2020-9-25

- 製品ニュース, 電気・電子系

- ESD, LDMOS, アナログIC, ジャパンセミコンダクター, セルレイアウト, 東芝デバイス&ストレージ

東芝デバイス&ストレージとジャパンセミコンダクターは2020年9月23日、アナログIC向けLDMOSの重要特性である負入力耐性とESD耐性を両立させる最適デザインを開発したと発表した。ESD耐性を許容できる水準を維持しつつ、これまでの同社の構造と比較して負入力耐性を40%向上させるという。

アナログICに搭載されるLDMOSは、高い信頼性の保持が求められているが、回生電流が流れた際に隣接回路への影響を抑える負入力耐性と、静電気によるデバイスの損傷や回路の誤動作を防ぐESD耐性が、特に重要な指標となっている。負入力耐性とESD耐性の向上には、チップサイズを大きくする施策がこれまで取られてきたが、製造コストの増加という課題があった。

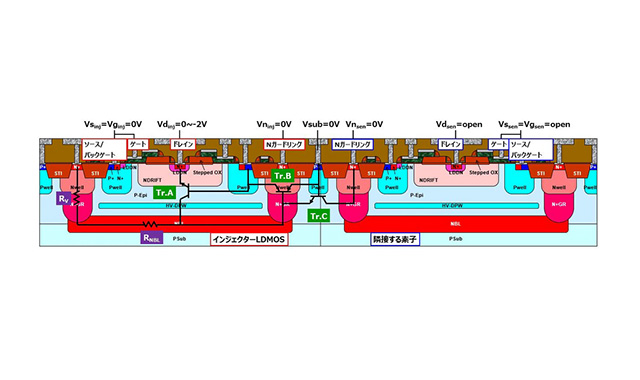

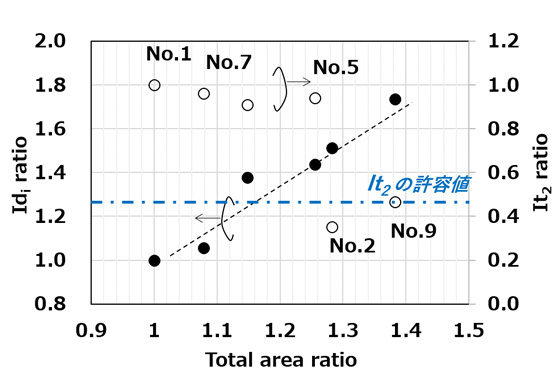

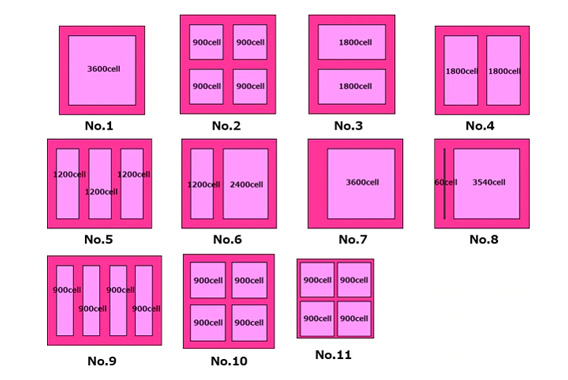

東芝デバイス&ストレージとジャパンセミコンダクターの両社は、インジェクターLDMOSのNガードリングでの抵抗が小さくなると負入力耐性が大きくなることに着目し、負入力耐性とESD耐性をさまざまなインジェクターLDMOSのセルレイアウトで検証。その結果、Nガードリングの幅を素子分割時の最大面積で割った変数が、負入力耐性と正の相関、ESD耐性と負の相関があり、両指標はトレードオフの関係にあることを発見したという。

負入力耐性とESD耐性の関係

このトレードオフの関係をもとに、最適だと考えられるLDMOSのセルレイアウト(下図No.10)を採用すると、素子面積の増大を15%、ESD耐性の劣化を9%に抑えながら、負入力耐性を40%向上できる。このセルレイアウトは、2019年度から量産している第四世代プロセスのLDMOSから適用できるという。

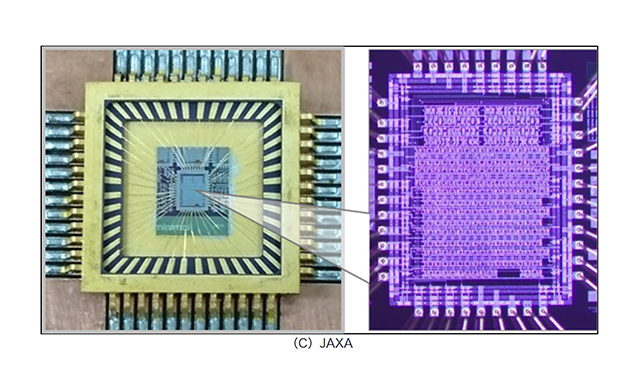

検証に用いたインジェクターLDMOSのセルレイアウト(濃いピンクはNガードリング、薄いピンクは素子内部)