- 2023-5-31

- ニュース, 技術ニュース, 電気・電子系

- 3D集積, Die-to-Wafer, IEEE 73rd Electronic Components and Technology Conference (ECTC2023), チップレット, チップレット集積, ディスコ, ハイブリッド接合, 仮接合, 剥離, 半導体, 東レエンジニアリング, 横浜国立大学, 研究

横浜国立大学は2023年5月30日、同大学工学研究院とディスコ、東レエンジニアリングの共同研究グループが、直接接合技術を用いる新たなチップ仮接合および剥離技術の開発に成功したと発表した。

微細化へのハードルが高まっている半導体デバイスの性能限界を突破する手法として、チップレット集積が近年注目されている。一方で、ウエハ上にチップを接合し、垂直方向の電気的な接続を担保する接合/配線技術には依然課題があり、新たな接合手法や集積手法が求められている。

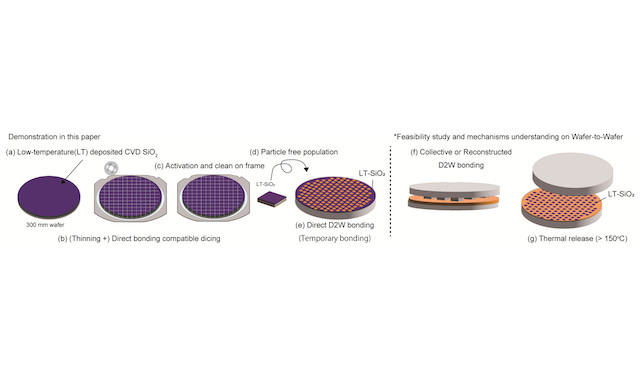

今回の研究では、新たに開発したCVD絶縁膜を用いて、ウエハ上にチップを仮接合した。プラズマ活性化ダイレクトボンディングによって仮接合するため、仮接合界面が多くの前工程プロセスとの互換性を有している。また、先端技術によるさらなる微細化なども見込める。

加えて、界面層が薄く固体であるため、ボンディング中にダイがずれるリスクを軽減できる。これによって、Die-to-Waferのハイブリッド接合を可能とし、仮接合による材料の加工時間や材料損失、コストの削減が可能となる。

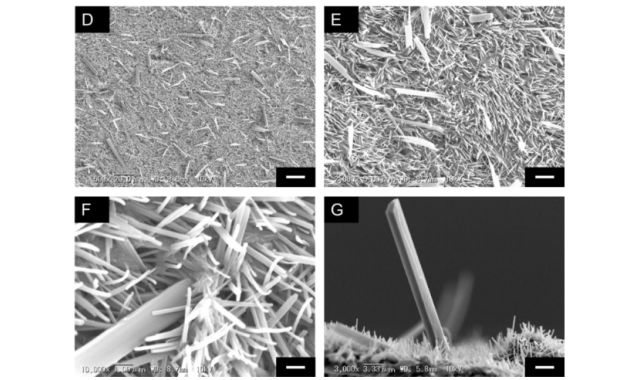

低温で堆積したSiO2膜によるボイド形成と、接合エネルギーの制御が仮接合の鍵となる。これらに向けて、表面粗さや膜組成、プラズマ活性化の影響、機械的特性を詳細に調査した。加えて、無水雰囲気でのボンディングエネルギー測定や界面空孔検査、TEM分析といった界面解析を実施した。

この結果、低温で堆積したSiO2が多くのオープンスペースや水を含んでおり、水の貯蔵層として機能し、ポストボンドアニール中に放出する可能性があることが判明した。これによって熱剥離が可能となり、少ない力でウエハとチップを容易に剥離できる。

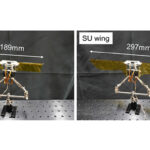

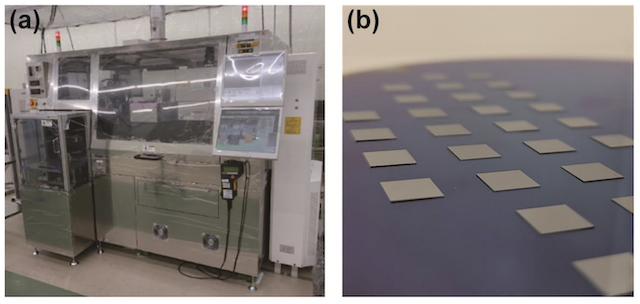

また、300mmウエハ上でのデモンストレーションも行った。異種3D集積の歩留り向上や高いボンディング位置合わせ精度、コスト削減に寄与することが期待される。

300mmウエハ上での実証実験の様子

同研究グループは、2023年5月30日から6月2日にかけて米フロリダで開催される半導体パッケージング技術の国際会議「IEEE 73rd Electronic Components and Technology Conference (ECTC2023)」にて同技術を公表する予定としている。