- 2023-6-15

- 化学・素材系, 技術ニュース, 海外ニュース

- 2D薄膜, AIアプリケーション, ChatGPT, CMOSウェハー, CMOS製造バックエンド配線形成工程(BEOL), MIT, MOCVDプロセス, Nature Nanotechnology, シリコンウェハー, トランジスタ, 二硫化モリブデン, 低温積層技術, 学術, 有機金属気相成長法, 自動会話プログラム, 遷移金属ジカルコゲナイド

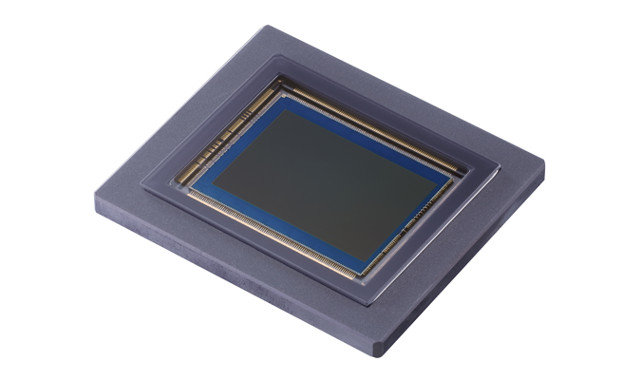

Credits:Image: Courtesy of the researchers

マサチューセッツ工科大学(MIT)の研究チームが、二硫化モリブデン(MoS2)の2D薄膜を、8インチCMOSウェハー上に直接成長させることができる低温積層技術を開発した。有機金属気相成長法(MOCVD)プロセスの反応炉において、MoS2の前駆体を分解する550℃以上の高温領域と、ウェハーチップ上にMoS2薄膜を積層する300℃以下の低温領域に分離することにより、高温によるシリコンチップの損傷を防ぎつつ2D薄膜を積層することに成功した。AIアプリケーションの急速な進展に対応して、コンピューターチップの高密度高性能化を達成できると期待している。研究成果が、2023年4月27日に『Nature Nanotechnology』誌に公開されている。

ChatGPTなどAIによる自動会話プログラムが急速に進化する中で、より高密度で高性能のコンピューターチップが求められるようになっている。一般的にコンピューターチップは3D構造のバルク材料で作製されており、多層から成るトランジスタを高密度に集積することは難しい。だが例えば、厚さ3原子程度の2D薄膜から構成されるトランジスタを、CMOS製造バックエンド配線形成工程(BEOL)において、シリコンチップウェハー上に直接積層できれば、高密度で高性能のチップを効率的に作製できる。

しかしながら、2D薄膜を直接シリコンウェハー上に成長させるには大きな問題がある。通常用いられるMOCVDなどのプロセスは、約600℃の処理が必要であるが、シリコンチップは400℃以上に加熱されると損傷してしまうからだ。研究チームはこれまで、2D薄膜を他で別途成長させた後、シリコンウェハー上に移送することを試みてきたが、2D薄膜をウェハースケールでスムースに移送するのは極めて難しい上、しばしば2D薄膜やシリコン回路に欠陥や汚染を発生させる問題があった。

研究チームは、チップを損傷しない新しい低温成長プロセスを開発して、遷移金属ジカルコゲナイドの1つであるMoS2の2D薄膜を、8インチ径シリコンCMOSウェハー上に直接成長させることに成功した。MOCVDプロセスにおいて、各々MoとSを含む2つの有機化合物前駆体を加熱気化させると、“分解”された分子の化学反応によってMoS2が表面上に“成長”するが、研究チームは分解工程と成長工程を分離して、BEOLに適した300℃以下の低温領域と分解に必要な550℃以上の高温領域を別々に設けた。

すると高温領域で分解された前駆体が低温領域に合流して、低温領域にセットされたウェハー表面上にMoS2を成長させることができた。高温によるシリコンウェハーの損傷を防止しながら、8インチ径ウェハー全体にわたって非常に均質で高性能な2D薄膜を得ることに成功したのである。加えて、2D薄膜の積層に要する時間を、従来の1日以上から1時間以下に短縮できることもわかった。

「8インチ以上のCMOSウェハーのBEOLに、多様な機能性を有する高品質2D薄膜を高速で直接積層するプロセスを統合できることは、実用化の観点からも大きな意味があり、半導体産業が2D材料を積極的に活用できる道を拓いた」と、研究チームは期待する。