- 2023-9-29

- 技術ニュース, 電気・電子系

- 3C-SiC, 4H-SiC, CHESS-MOSR, CUSIC, SiC, SiCパワー半導体, SLE法, ハイブリッド構造基板, 同時横方向エピタキシャル成長法, 東北大学, 東北大学未来科学技術共同研究センター, 東北大学電気通信研究所, 研究

東北大学電気通信研究所と同大学未来科学技術共同研究センターは2023年9月28日、CUSICと共同で、世界で初めて、同時横方向エピタキシャル成長法(SLE法)を用いて、3C-SiCと4H-SiCを積層させたハイブリッド構造基板を製作したと発表した。4H-SiC表面の200分の1以下まで3C-SiC表面の密度を低減できることを実証している。

SiCパワー半導体デバイスは、世界中で実用化が進められているが、SiC単結晶の物性そのものに由来する根本的な問題を克服する新技術の開発が求められている。

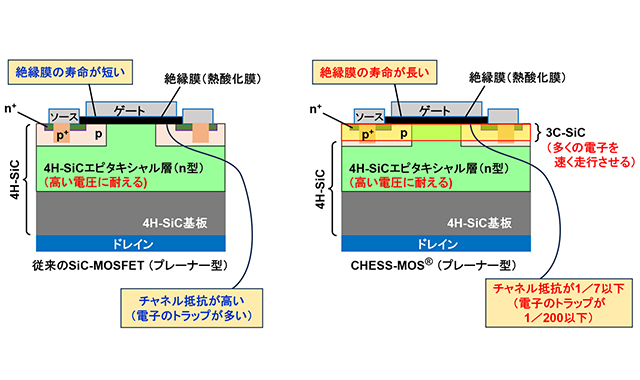

CUSICは、SiCパワー半導体デバイスの電力損失低減と長期信頼性確保を同時に実現する技術として、新しいパワー半導体デバイス(CHESS-MOS)を考案した。CHESS-MOSは、同じSiC単結晶でありながら異なる結晶構造と物性値を持つ、3C-SiCと4H-SiCを積層させたハイブリッド構造基板で実現されるもので、SiC単結晶の問題を克服する有力候補となっていた。

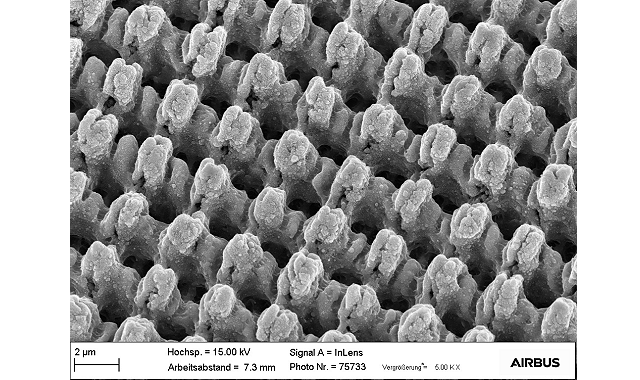

研究グループは、CHESS-MOSの実現に向けた共同研究を進める中で、世界で初めて、3CSiCと4H-SiCを積層させたハイブリッド構造基板をSLE法を用いて製作した。

また、走査型非線形誘電率顕微鏡法(SNDM法)で、絶縁膜(熱酸化膜)を形成したハイブリッド構造基板表面の界面準位密度を計測し、SLE法で界面準位密度を大幅に低減できることを実証した。これらの結果と過去の知見から、低い界面準位密度の達成により、CHESS-MOSを取り入れることで、電力損失を30%以上削減できる見通しとなる。

SLE法は、1原子分の高さの狂いもなく3C-SiC層と4H-SiC基板の界面が平坦に形成される特長があるため、3C-SiC層内の自由電子は、界面近傍を散乱されずに高速に走行でき、さらなる電力損失低減と高速動作につながることが期待される。

また、3C-SiCは、4H-SiCよりも大きな電子親和力を有するため、CHESS-MOSの絶縁膜/SiC界面に形成される電子に対する障壁は、4H-SiCよりも圧倒的に高くなると考えられる。これにより、大幅にSiCパワー半導体デバイスの長期信頼性が向上し、SiCパワー半導体デバイスを用いたアプリケーションの市場拡大が期待される。

さらに、SLE法の実験で、3C-SiC/4H-SiC/3C-SiC/4H-SiCのような二重量子井戸構造が形成される現象も確認された。意図的にこうしたSiC積層構造を形成することで、SiC半導体デバイスではこれまで困難だと考えられていた高周波デバイスが実現する可能性がある。

高周波信号減衰の問題を回避できるため、既存のSiCパワー半導体デバイス生産ライン用いた高周波集積回路の量産への道も考えられる。さらに、高温下や放射線にさらされる宇宙空間、原発廃炉作業場でも長期信頼性に優れた集積回路の実現が期待される。

関連情報

結晶構造が異なるSiC同士のシームレスな積層に成功… | プレスリリース・研究成果 | 東北大学 -TOHOKU UNIVERSITY-